3DInCites<sup>TM</sup> EST. 2009

# The First Decade

**Page 27** The Past, Present

and Future of 3D Integration

**Page 36** Ten Years of

Invent, Innovate, Implement

**Page 62** The First

Decade in Pictures

invent

innovate

implement

[www.EVGroup.com](http://www.EVGroup.com)

## BREAKTHROUGH ALIGNMENT ACCURACY FOR 3D DEVICE STACKING

■ Introducing the new SmartView® NT3 with sub-50 nm alignment accuracy on the GEMINI® FB XT bonding platform

■ Fusion and hybrid wafer bonding enables leading-edge 3D Stacked CIS, Memory Stacking and 3D SoC devices

GET IN TOUCH to discuss your manufacturing needs

[www.EVGroup.com](http://www.EVGroup.com)

GEMINI® FB XT

# CONTENTS

**27**

## **The Past, Present, and Future of 3D Integration**

In this special section, industry experts talk about pivotal moments and future expectations for 3D and heterogeneous integration.

**27**

### **3D InCites Turns 10: A Brief Analysis of the 3D Journey**

Yann Guillou, Trymax

**28**

### **3D Powered: From Image Sensors to Edge Computing**

Paul Werbaneth, Nor-Cal Products, Inc.

**29**

### **3D Integration's Thousand Mile Journey**

Amy Leong, FormFactor

**29**

### **3D Enables More than Moore**

Paul Lindner, Executive Technology Director, EV Group

**30**

### **A Shift in Value from Single to Multi-die ICs**

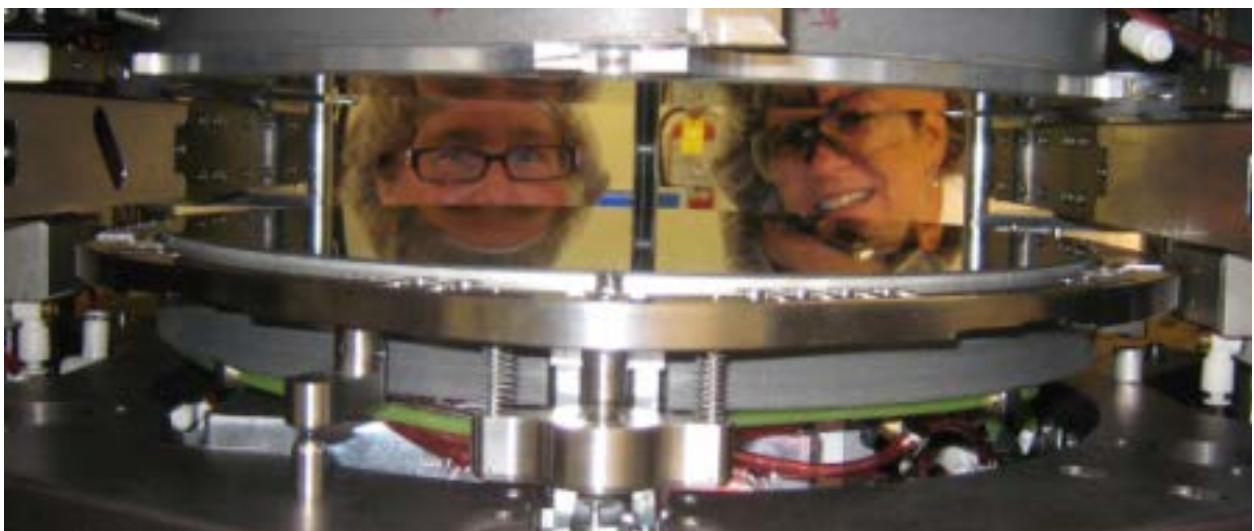

Herb Reiter, eda2asic

**31**

### **Eliminating the Memory Wall**

Jan Vardaman, TechSearch International, Inc.

**32**

### **From 3D Pioneers to 3D Robots**

Dr. Phil Garrou, IFTLE, Microelectronics Consultants of North America

**32**

### **Thank 2.5D Interposers for the Success of 3D ICs**

Mark Scannell, CEA-Leti

**34**

### **Heterogeneous Integration Calls for Increased Materials Reliability**

Dr. Andy C. Mackie, PhD, Indium Corporation

**34**

### **Extending Moore's Law through Advanced Packaging**

Carl McMahon, Genmark Automation

**36**

## **ON THE COVER:**

### **10 Years of Invent, Innovate, Implement**

Françoise von Trapp returns to EV Group for her fourth visit and reminisces about the past 10 years.

**8**

## **FEATURES**

### **Hybrid Bonding: From Concept to Commercialization**

An interview with Xperi's Gil Fountain

**12**

### **Advanced Packaging: An IFTLE Historical Perspective**

By Dr. Phil Garrou, Microelectronics Consultants of NC

**16**

### **Why Today's Advanced Packages Need Better Inspection**

By Françoise von Trapp

**19**

### **Diversification of Markets Calls for Hybrid Metrology with Multi-Sensor Technology**

An interview with Thomas Fries, FRT- The Art of Metrology

**21**

### **3D Test - No Longer a Bottleneck!**

By Eric Jan Marinissen, imec

**43**

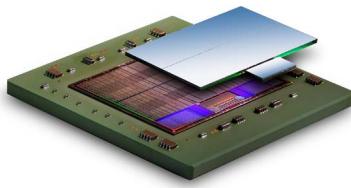

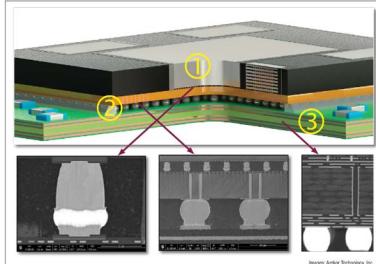

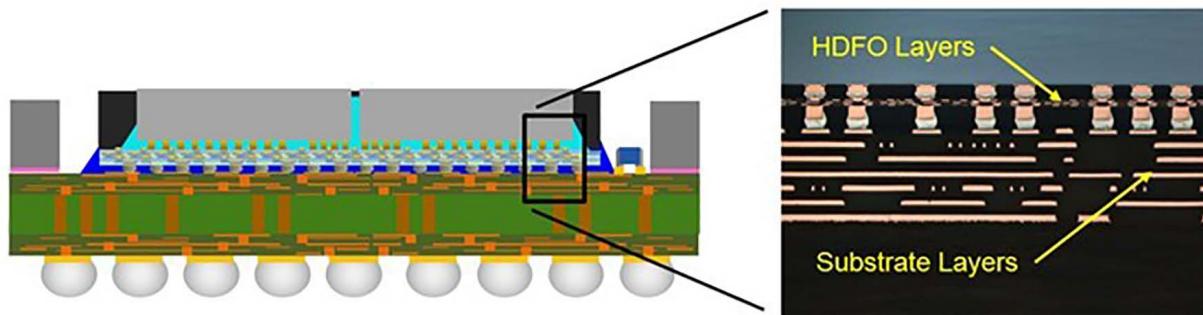

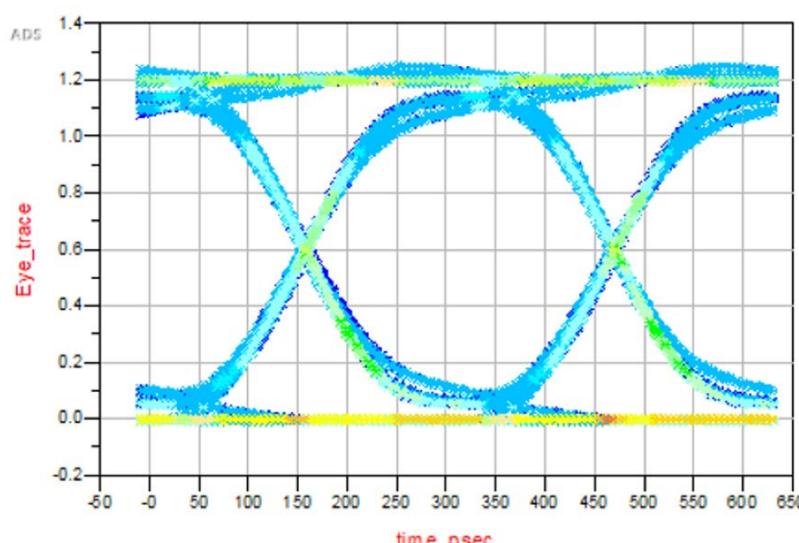

### **Advanced Heterogeneous Packaging Solutions for High-Performance Computing**

By Ron Huemoeller, Mike Kelly, Curtis Zwenger, Dave Hiner, and George Scott, Amkor Technology, Inc.

# CONTENTS CONTINUED

**45**

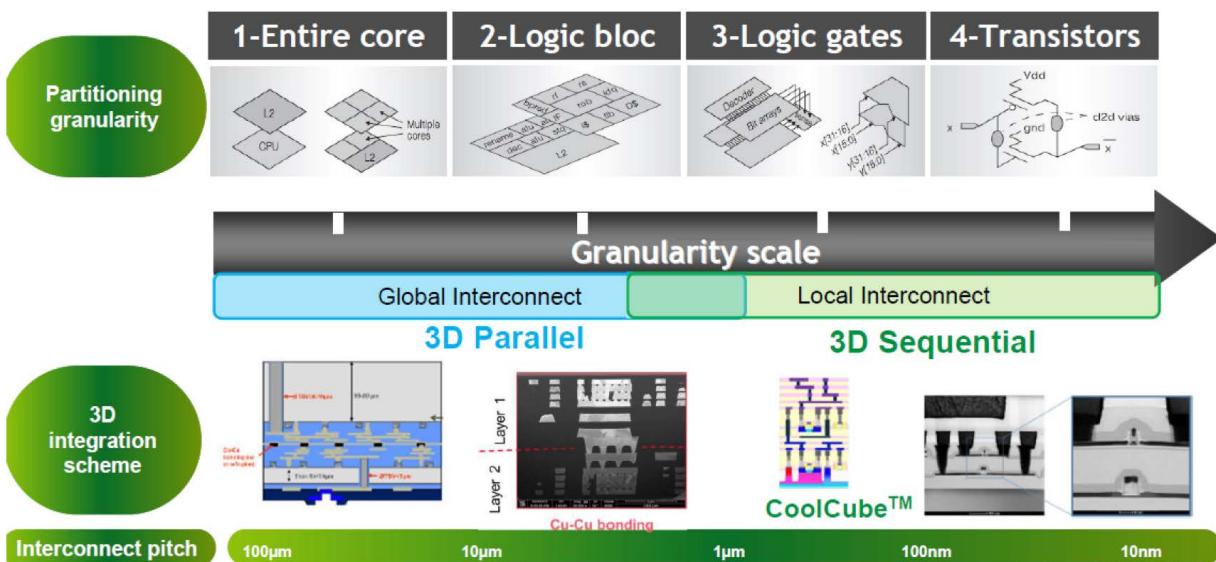

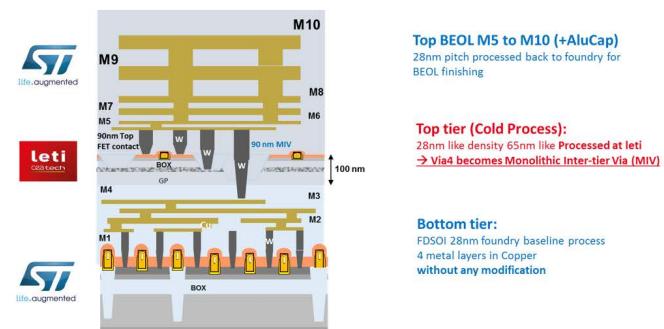

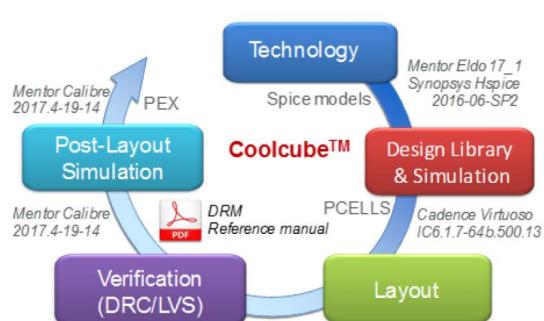

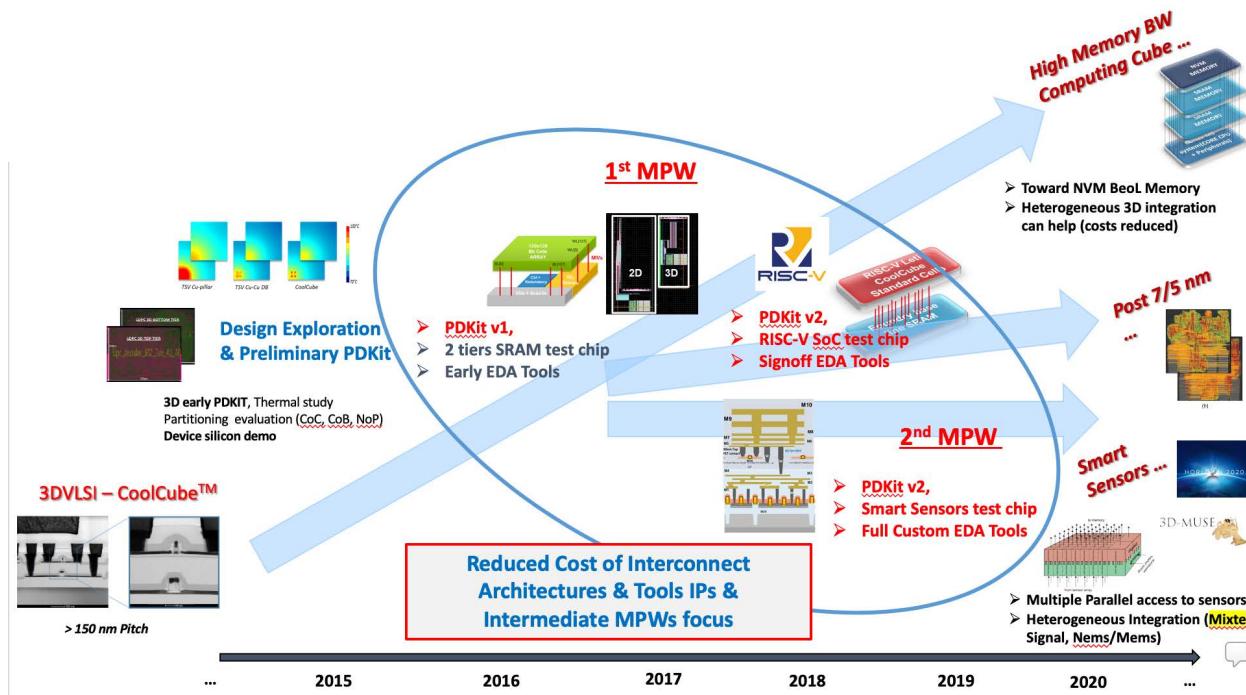

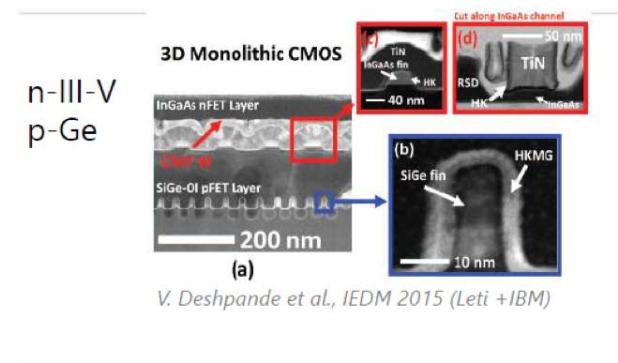

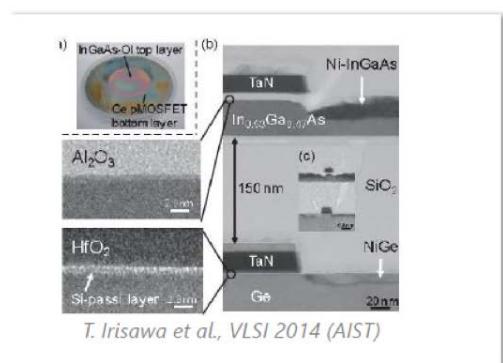

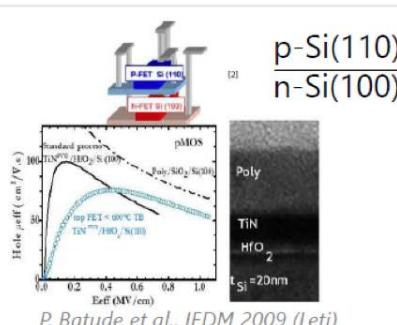

- CoolCube™: Much more than a True 3DVLSI Alternative to Scaling**

By Jean-Eric Michalette, CEA-Leti

**53**

- Addressing the Challenges of Surface Preparation for Advanced Wafer Level Packaging**

Q&A featuring Anil Vijayendran, Veeco Instruments

**55**

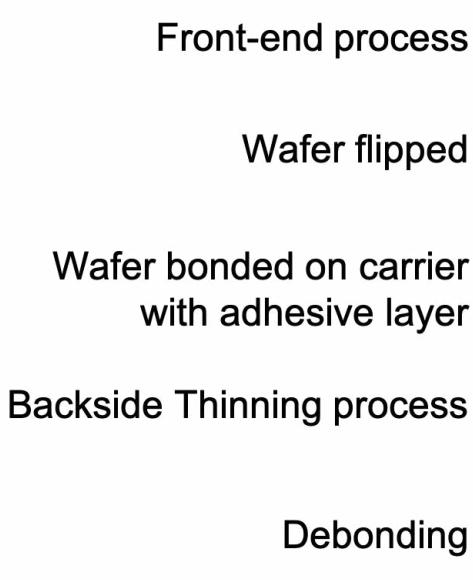

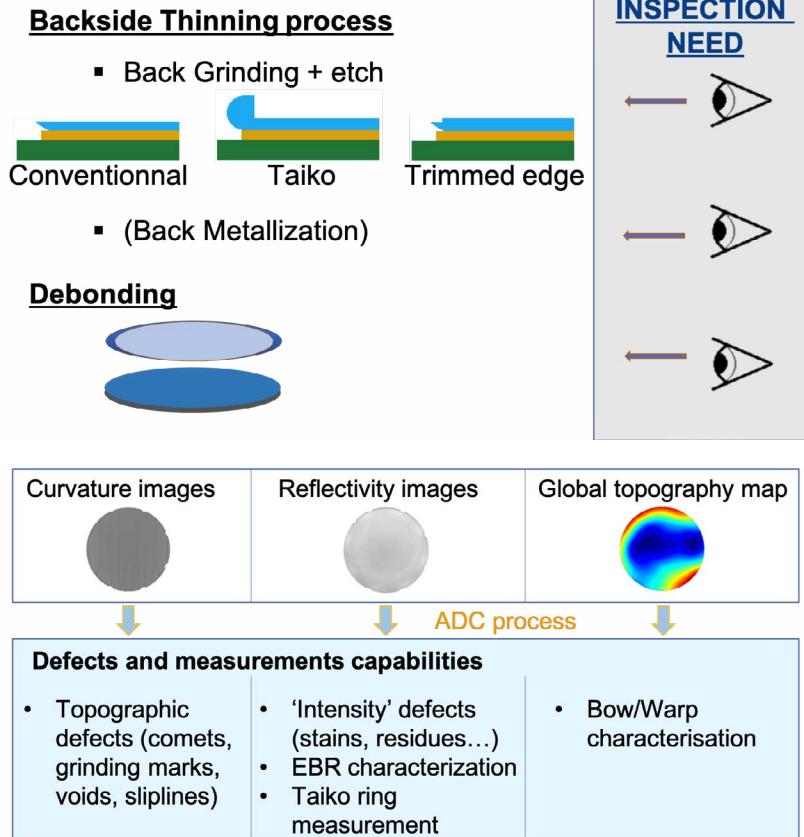

- Reliable Process Control Solutions for the Growing Power Device Market**

By Dr. Dario Alliata, Unity-SC

**57**

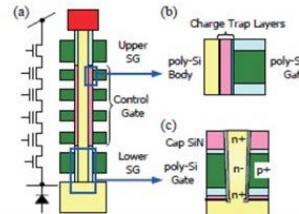

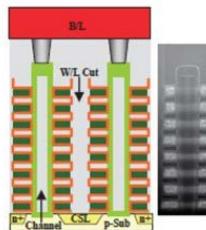

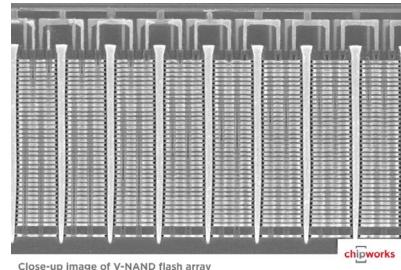

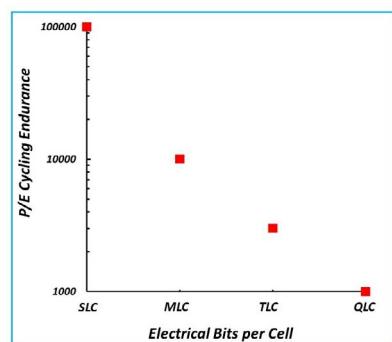

- 3D NAND: Where Haste You So?**

By Andrew Walker, Schiltron, Corp.

**62**

**The First Decade in Pictures**

3D InCites has always been about the people in our industry. Here is a collection of photos from throughout the years.

## STAFF

**Françoise von Trapp,

Editor-in-Chief**

Francoise@3DInCites.com

Ph: 978.340.0773

**Martijn Pierik, Publisher

Martijn@3DInCites.com**

Ph: 602.366.5599

**Danielle Friedman,

Director of Operations**

Danielle@3DInCites.com

Ph: 602.443.0030

**Phil Garrou, Contributing Editor**

PhilGarrou@att.net

**Herb Reiter, Contributing Editor**

Herb@eda2asic.com

**Creative/Production/Online**

**Rose Rover,**

Production Manager

**Taylor Lineberger,**

Lead Designer

**Juan Pence,**

Lead Web Designer/Developer

**Ale Moreno,**

Web Developer

**Technical Advisory Board**

**Sitaram R. Arkalgud, Ph.D.,**

Xperi Corporation, USA

**Rozalia Beica,**

DowDupont, USA

**Pascal Couderc,**

3D PLUS, France

**Yann Guillou,**

Trymax Semiconductor,

Netherlands

**Dr. Phil Garrou,**

Microelectronic Consultants

of NC, USA

**Erik Jan Marinissen,**

Principal Scientist at IMEC, Belgium

**Peter Ramm,**

Fraunhofer EMFT, Germany

**Herb Reiter,**

eda2asic Consulting, USA

**Mark Scannell,**

Leti, France

**Dr. Maaike M. Visser Taklo,**

Disruptive Technologies, Norway

**E. Jan Vardaman,**

TechSearch International, Inc.

**Paul Werbaneth,**

Nor-Cal Products, Inc.

**M. Juergen Wolf,**

Fraunhofer IZM-ASSID, Germany

**Visit us at [www.3DInCites.com](http://www.3DInCites.com)**

Subscribe to our e-newsletter,

3D InCites In Review: <https://www.3dincites.com/subscribe-newsletter/>

3D InCites: The First Decade was

published by:

3D InCites, LLC

45 West Jackson St. Suite 700

Phoenix, AZ, 85003

Ph: 602.443.0030

Copyright ©2019 by 3D InCites,

LLC. All rights reserved. Printed in

the US.

# WE'RE IN THE PACKAGING BUSINESS TOO.

Just as important as the technology you create is how you package and market it to the world. At Kiterocket, we deliver professional, well-branded communications that help bring products to life.

Are your marketing efforts well packaged? Let Kiterocket develop the right program to propel your business.

# Advanced Packaging at Amkor

More Devices.

More Data.

More Applications.

[www.amkor.com](http://www.amkor.com) ► [sales@amkor.com](mailto:sales@amkor.com)

Enabling the Future

# A Message from the Queen of 3D

Has it already been 10 years since my first business partner, Leo Archer, and I started 3D InCites?

When we first conceived of the idea in 2009, I had no idea what I was getting myself into or that 10 years later, 3D InCites would be so well recognized in the industry.

Leo and I parted ways in 2011, and in 2012, I partnered with Martijn Pierik and Dave Richardson of Impress Labs (now Kiterocket). Bolstered by the support of these two partners and a web design and development team, I was able to focus on creating valuable content and building a following. I remember how excited I was when, in our first year, we hit 116 registered members. Ten years later, we log in over 80K users annually.

Putting this 10th Anniversary issue together has been a nostalgia trip for me, from searching through the archives and photos, to reading all the contributions from our friends in the industry. For that is how I think of all of you: not just readers, but a community of colleagues.

3D InCites has always been more than just another source of technology news and information. Perhaps Rajiv Roy, FormFactor, said it best in a testimonial: "As a community, 3D InCites brings to life the people, the personalities, and the minds

behind 3D integration in a uniquely personal way." It's what sets us apart from the other industry publications, and we live by it. The past 10 years have been full of pivotal moments for the companies and people responsible for developing 3D and heterogeneous integration technologies, and 3D InCites has been lucky to grow up alongside it.

We were there when the EMC3D Consortium put TSVs on the roadmap, and drove cost reduction efforts to bring them to commercialization. We were there when imec, CEA-Leti, SEMATECH, Fraunhofer EMFT, Fraunhofer IZM-ASSID, and others developed back-end processes that are now mainstream.

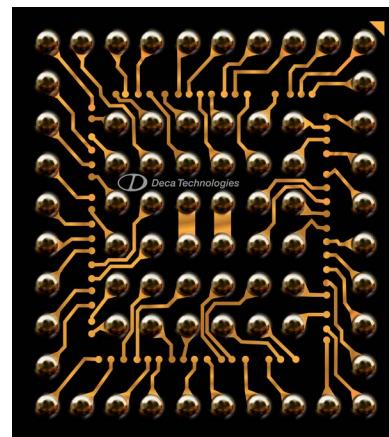

We were there when companies like Alchimer, ALLVIA, NEXX Systems, Replisaurus, Tezzaron, and Ziptronix were just getting started. We were there for the launches of Deca Technologies, Invensas, KOBUS, and UnitySC. We remember when Alchimer became Aveni, and when Replisaurus went the way of the dinosaurs; and when Ziptronix was acquired by Invensas, and then became Xperi. We remember when Applied Materials and TEL almost became Etaris, and then didn't.

In 2013, we created the 3D InCites Awards to recognize the contributions people, companies, and

research institutes have made to bring about the commercialization of 3D and heterogeneous integration technologies. This year marks the 7th year of the awards program. Our statue graces the award cases of Amkor Technology, Inc.; Brewer Science; Bob Patti; Bryan Black; Deca Technologies; Dow Corning (now Dupont); Dusan Petranovic; E-System Design; EV Group; and Fogale Nanotech (now UnitySC); Fraunhofer IZM; Fraunhofer Cluster for 3D Integration; FRT, the Art of Metrology; Gill Fountain; GLOBAL-FOUNDRIES; KLA; Kobus (now part of PlasmaTherm); imec; Mentor, A Siemens company; OmniVision; Novati Technologies; Paul Enquist; Phil Garrou; Semblant/HZO; SPTS; Sorin CRM; SSEC (now Veeco); TSMC; Xilinx; and Xperi.

Thanks to your sponsorship and donations, we've made significant contributions to the IEEE Women in Engineering Scholarship, SEMI High Tech U, the IMAPS Foundation, G1ve-A-Buck, and Phoenix Children's Hospital.

What does the future hold? 3D integration has finally hit the big time, and we'll continue to bring you the latest developments. Some of them are in this issue. In October 2018, Phil Garrou joined us as a contributing editor, bringing with him his well-known blog, rechristened Packaging InCites from the Leading Edge. He joins Herb Reiter, our EDA expert, as a regular contributor. We've also launched the SemiSister project to support gender diversity and inclusion efforts in the semiconductor industry.

In 2019, the 3D InCites leadership changed again. Dave Richardson has gone on to pursue other interests, leaving Martijn and me at the helm of this particular ship. We are excited for what the next 10 years has in store, and we hope this issue takes you on your own walk down memory lane.

# Hybrid Bonding: From Concept to Commercialization

**By Françoise von Trapp**

Hybrid bonding is quickly becoming recognized as the preferred permanent bonding path for forming high-density interconnects in heterogeneous integration applications, from 2.5D to 3D stacking with or without through silicon vias (TSVs), as well as MEMS and III-V applications. In this exclusive interview with Gill Fountain, Xperi, winner of the 2018 3DInCites Engineer of the Year award for his work in this area, we embark on the journey of how one hybrid bonding technology came to be.

## What Do We Mean by Hybrid Bonding?

A quick Google search shows that the semiconductor industry has used the term “hybrid bonding” loosely to refer to any alternative to thermocompression bonding that combines metal interconnect with some other form of bonding. In some cases, it includes adhesives, such as work done by imec and its partners, and by a team at Dalian University of Technology in China.<sup>1</sup>

In other cases, it involves various interconnect metals such as copper (Cu), indium (In), and silver (Ag). One example is solid-liquid inter-diffusion (SLID) developed by Fraunhofer Institute.<sup>2</sup> Another example is a binary bonding approach that uses InAg combined with atmospheric plasma surface activation, developed by SET-NA.<sup>3</sup>

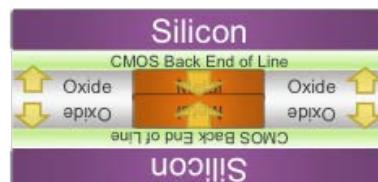

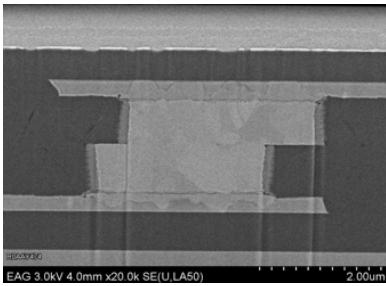

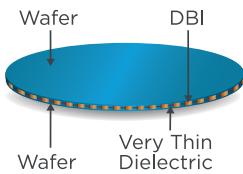

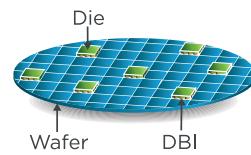

For the context of this interview, hybrid bonding is defined as a permanent bond that combines a dielectric bond with embedded metal to form interconnections. It's become known industry-wide as direct bond interconnect, or DBI™ (Figure 1).

## The early days: developing ZiBond

As Fountain tells it, the DBI story began 20 years ago in the labs at Research Triangle Institute (RTI), when his colleague, Paul Enquist,

### Oxide to oxide initial bond at room temperature

### Heating Closes Dishing Gap (Metal CTE > Oxide CTE)

### Further Heating Compresses Metal w/out External Pressure

Figure 1: DBI bonding process

needed a bonding solution that would allow for fine-line lithography after bonding. The pair turned to Q.Y. Tong, described by Fountain as “the leading guru in wafer bonding”, and then manager of RTI’s wafer bonding lab. Together over the next few years, they developed and patented ZiBond®, an enhanced version of direct oxide bond that involves wafer-to-wafer processing at low temperatures (150-300°C) to initiate high bond strength rivaling silicon.

“What differentiates ZiBond from other direct oxide bonds? “It’s not

just an oxide bond,” explained Fountain. “ZiBond requires the wafer or die surface preparation to be done in such a way that you reach a certain bond strength at a certain temperature.” Exactly what those parameters are is part of the secret sauce. ZiBond is the dielectric bond that forms the basis for DBI.

### Ziptronix and the Road to DBI

Armed with the ZiBond patent, Fountain, Enquist, Tong and several other colleagues founded Ziptronix in 2000 as a spin-out of RTI. What was Fountain’s vision for the company next? To combine the dielectric bond with embedded metal to simultaneously bond wafers and form the interconnects.

He gives Enquist most of the credit. “Paul was the guy with the vision. I was just the guy in the lab turning the cranks,” he says.

I compared them to Woz and Jobs. He laughs and says, “Paul is a brilliant guy with a lot of good ideas. He has a feel for what would be good for the industry.”

At the time, the holy grail of 3D stacking was how to stack parts and form the interconnect as part of the bond process at finer pitches than was currently possible using wire bonding. Early prototypes involved cleaning and mounting dies on wafers using ZiBond, and then forming the top connections or through the back of wafer with “brute force” methods to connect bond pad to bond pad. Fountain noted that Sony dabbled in this staple-like approach, but the structures were big. They needed to find a more compact and efficient way to make these connections.

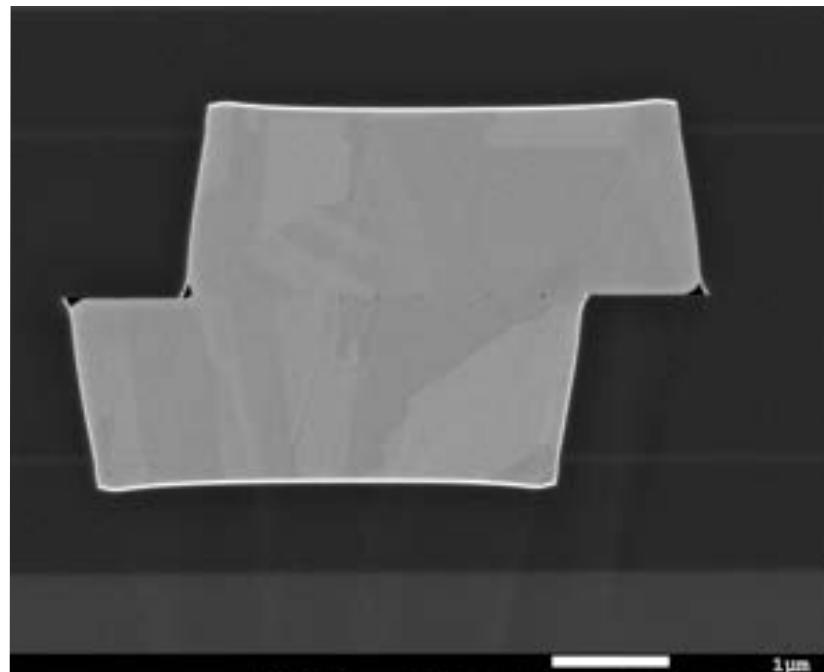

Fast forward to 2005 and the emergence of DBI (Figure 2). The solution was to start with an oxide bond with embedded metal recessed into it. Heat forces the metal together because it expands more than the oxide, causing it to bond, explained Fountain. Initially, nickel was the contact material used because it polished well with oxide, and some

Figure 2: 10µm pitch Ni DBI daisy chain connection with Aluminum routing layer (Ziptronix 2010)

Figure 3: 2µm pitch Cu DBI wafer to wafer stack (Ziptronix 2011)

are still using it. The first applications to implement DBI were small pitch parts for focal plane arrays. They had to reach sub 10µm pitch with 3µm diameter pads.

### Addressing the Challenges

As foundries don't like to work with nickel, it was important to get Cu to work with the process. The biggest challenge involved surface cleaning and achieving surface topology (Figure 3).

"Adhesives are tolerant of particles," explained Fountain. "DBI requires

particle-free clean surfaces. Additionally, the surface and oxide must be smooth, and the metal has to be slightly below the surface."

The team figured a few things out along the journey, like what materials worked best for Cu and barrier polish and played around with pushing temperatures as low as possible to expand the process window to more applications, such as memory and compound semiconductors.

"We found that we could readily address engineering challenges associated with cleaning and damascene utilizing the existing equipment sets in foundries today," noted Fountain. "Damascene copper is their bread and butter. To complete the fabrication process with a surface that can be bonded seems like a natural progression."

### Advantages of DBI

Fountain says DBI overcomes many of the process challenges that plague TCB, such as alignment, and bond strength at tighter pitches. The initial bond forms instantaneously, the alignment of the parts work well, and they don't slip or move as the bond is strengthened during the low-temperature annealing process. Moreover, the annealing process can be done in batches later, which speeds up the process and improves throughput.

With TCB, parts have to be held in

place while heating. DBI is limited only by the alignment capabilities of the bonding tool. 1.5µm pitch is the tightest so far at the die level, but that's because the tools can't go smaller, explained Fountain. Moreover, the final bond is stronger because unlike TCB, the bond forms at both the oxide and metal interfaces, not the metal only.

Other approaches to hybrid bonding that call for adhesives or mixed metals don't form as strong a bond as a single metal, explained Fountain. Adhesives can cause reliability issues due to thermal cycling. Additionally, the bond is hermetic, which positively impacts the reliability of the end device.

### DBI's Journey to Adoption

Despite its elegance, it took a while for DBI to take off. Fountain attributes that mainly to the industry's resistance to change. Early adopters had a need that wasn't being met in other ways. For example, Sony was building its image sensors with adhesives and reached distortion limits with lithography.

"We put a lot of work into this technology because we wanted to see it become a useful platform for the industry. It made sense to me that Moore's law would be expanded by going vertical. Having efficient ways to combine things would be the way of the future," noted Fountain. "We were a bit ahead of our time,

and it took a while to get traction with the technology. But now we are seeing more and more adopters in the industry."

### The Journey Continues

Several licenses and an acquisition in 2015 by Tessera Technologies (now Xperi) later, Fountain and his team continue to improve DBI, not only to better understand the polishing processes but to achieve ever-changing device requirements so that it can handle a wide range of applications and pitch sizes.

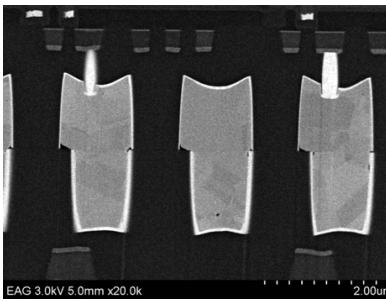

Most recently, Fountain and his colleagues are working on scalable high-volume die-to-wafer bonding, working with different pitch and pad sizes to accommodate high-speed pick-and-place tools that have only 7-9 $\mu$ m alignment accuracy, and a double-sided die preparation process to enable sequential stacking for the memory market.

"DBI worked easily at smaller pitches and pad sizes because Cu dishing isn't an issue. With larger pad sizes it's more difficult to get appropriate dishing and a flat oxide surface," explained Fountain. "We've expanded the size of pads we can polish to 15-20 $\mu$ m." Metrology for surface topography check has been key to this development work, he added, crediting his atomic force microscope as the core tool for this work (Figure 4).

### The Million Dollar Question

Will DBI become process of record (POR) across all 3D IC stacking approaches? Fountain is con-

Figure 5: 10 $\mu$ m pitch Cu DBI after 2000 temperature cycles of -40°C to 150°C (Xperi 2018)

dent that it can and ticked off the reasons why: It's compatible with foundry processes, and parts can be prepared for bonding right off the line in the fab or OSAT. It can handle fine or large features (Figure 5). Its reliability is good for thermal cycling, high-temperature storage, and high humidity, which is why it's suited to automotive applications.

"It's got a lot of potential. It's what I've known and grown up with my whole career. I have a lot of confidence in it. I've seen it do amazing things and have high hopes for its use in the future," said Fountain.

"The fact that a little place in North Carolina could have come up with

something that is valuable to a company like Sony just blows my mind," he added.

Yes indeed. Now I know why Gill Fountain was voted Engineer of the Year. Well done. ~ FvT

### References

1. M. Yao, J. Fan, N. Zhao, "Simplified low-temperature wafer-level hybrid bonding using pillar bump and photosensitive adhesive for three-dimensional integrated circuit integration", Journal of Materials Science: Materials in Electronics, January 28, 2017 1149-1150

2. P. Ramm, Understanding Heterogeneous 3D Integration, 3DInCites, January 16, 2015

3. E. Schulte, M. Lueck, A. Huffman, C. Gregory, K. Cooper, D. Temple, Interconnect structure for room temperature 3D IC stacking employing binary alloying for high-temperature stability. Proc. IW

Figure 4: high DBI Die to wafer stack with 50 $\mu$ m thick die processed at Xperi

# Platform Portfolio

## METROLOGY

### TMAP

for Adv. Packaging

and MEMS

### NST

for hybrid bonding

### AXIO

Review and

Metrology

### ODIN

F/B MICRO AOI

### WOTAN

F/B MACRO AOI

### THOR

Edge AOI

### 4 SEE

Full Inspection system developed

for Wafer manufacturers and Power

Semi manufacturers.

# Advanced Packaging: An IFTLE Historical Perspective

By Dr. Philip Garrou, Microelectronic Consultants of NC

On this 10th Anniversary of 3DInCites, I thought it would be a good idea for Packaging InCites from the Leading Edge (IFTLE) to look back at advanced packaging's evolution through 50 years and see how we came to be where we are.

## The point of the package

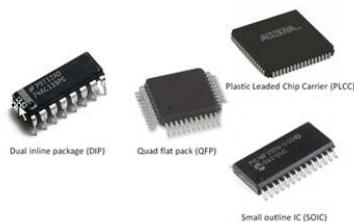

From the beginning, packaging has been subservient to the integrated circuits (ICs) that they contain. As ICs became more complex, so too did the packaging and interconnect technologies that allowed the chips to be connected and create circuits to accomplish specific tasks.

The chip's package must always provide:

- Circuit protection / handling

- Form factor for testing

- Heat dissipation

- Signal and power distribution

While the dimensions on ICs have continued to shrink year over year in accordance with Moore's Law, dimensions on printed circuit boards (PCBs), where the pack-

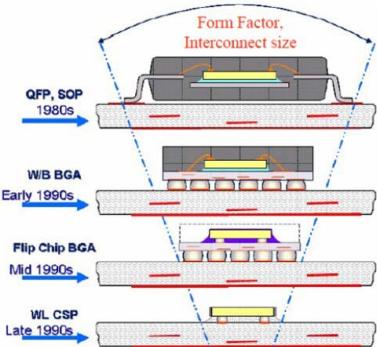

Figure 2: Peripheral Lead frame packages evolve to the BGA

Figure 1: Packaging evolution through the decades

aged chips are interconnected, have not been able to keep pace. Thus, the package must also serve as a "space transformer" (i.e. an "interposer") to bridge the gap between the connection pads on the chip and the connection pads on the PCB, which are usually miss-matched by at least an order of magnitude.

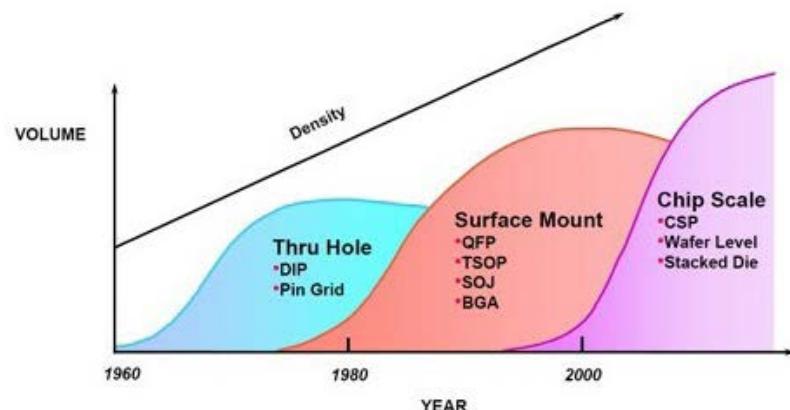

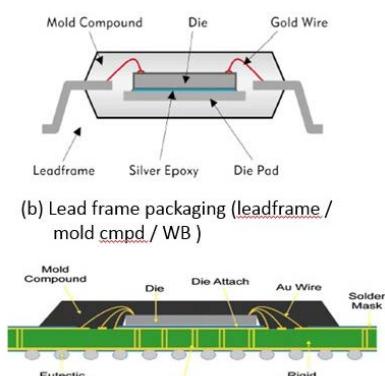

As shown in Figure 1, as we approached the 21st century, chip interconnection evolved through three distinct generations. Initially chips were mounted on lead frames and the leads inserted into holes on the PCB and soldered in place. In the surface mount technology (SMT) era in the 1980s-90s, the leads were bent into the horizontal plane, so the chips could be soldered to connection pads which were formed on the PCB, to make assembly much more cost efficient (Figure 2A-C).

## From wire bond to flip chip

Packaging technology continued to evolve through the decades to meet miniaturization requirements, while at the same time offering more input/output (I/O) by moving from peripheral wire bonded (WB) technology to area array connection technology. Packages initially used WB, and thus the leads existed only on the chip's periphery. The package size was thus determined by the required number of leads and their pitch.

As ICs evolved, more I/O were required than could be accommodated on the periphery (at a usable pitch), which necessitated a change from peripheral to area array formats, affording many more I/O at the same pitch. During the SMT era, this led to the commercialization of the ball grid array (BGA) package which functioned to

Figure 3: SMT lead frame packages evolved to the WLP.

fan out the IC pitch to an area array (Figure 2D).

Ideally, the IC package should be small and add as little additional interconnect length as possible (to minimize electrical performance degradation). Flip chip (FC) interconnect technology enabled smaller overall package sizes, an area array interconnect footprint, and improved electrical performance.

The concept of interconnecting a chip with solder bumps in an area array can be traced back to IBM's introduction of their system 360 mainframe computer in 1964. For several decades after, flip chip was confined to high-end main frame computer companies like IBM, NEC, Fujitsu, and Hitachi because it was limited to ceramic packaging due to the mismatch between the coefficient of thermal expansion (CTE) of Si and the PCB substrate [3 ppm/ $^{\circ}$ C vs. 16 ppm/ $^{\circ}$ C (FR4)].

In 1992, Tsukada of IBM Japan published reports that bumped chips could be reliably attached directly to printed wire board laminate if the chips were under-filled. This announcement drove the packaging community to take a hard look at flip chip technology in a broader application space. By the mid-1990s Motorola had introduced flip chip on board (FCOB) into the StarTac handset.

By the mid-1990s the miniaturization required by cell phones and other portable products created demand for a "chip scale package" (CSP) also called wafer level chip scale package (WLCSP), or more simply, the wafer-level package (WLP). In WLP technology small

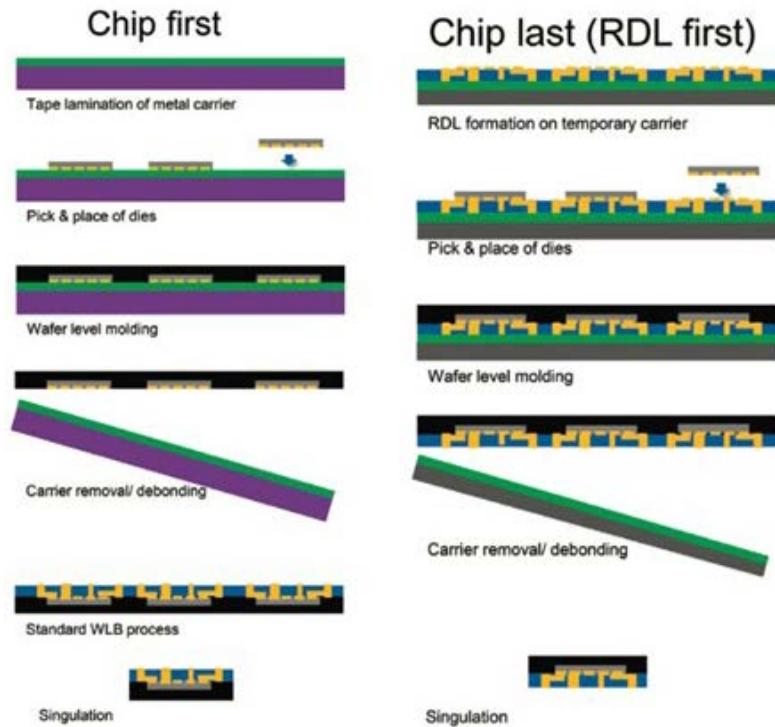

Figure 4: Chips-first and chips-last fan-out packaging

chips are bumped with the correct size and pitch bumps to allow them to be directly mounted onto PCBs without further packaging.

Since all I/O in WLCSP had to exist under the chip, the package technology soon became I/O limited. Once miniaturization reached chip size it had two options for future advancement.

For option one, the industry developed a series of packages that were called "fan-out". Fan-out WLP (FOWLP) is "re-configured" by placing known-good ICs face down on a foil and over-molding them. These molded wafers are then flipped and processed in the wafer fab with redistribution layer (RDL)/ball placement and diced. Alternatively, the interconnect is created first, and the

die is connected after the interconnect is formed (Figure 4).

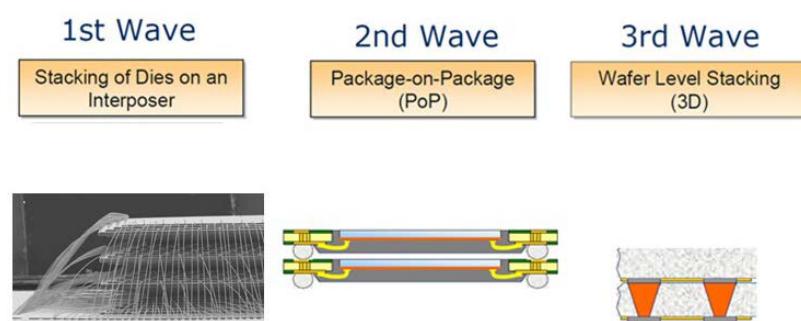

### Packaging goes vertical

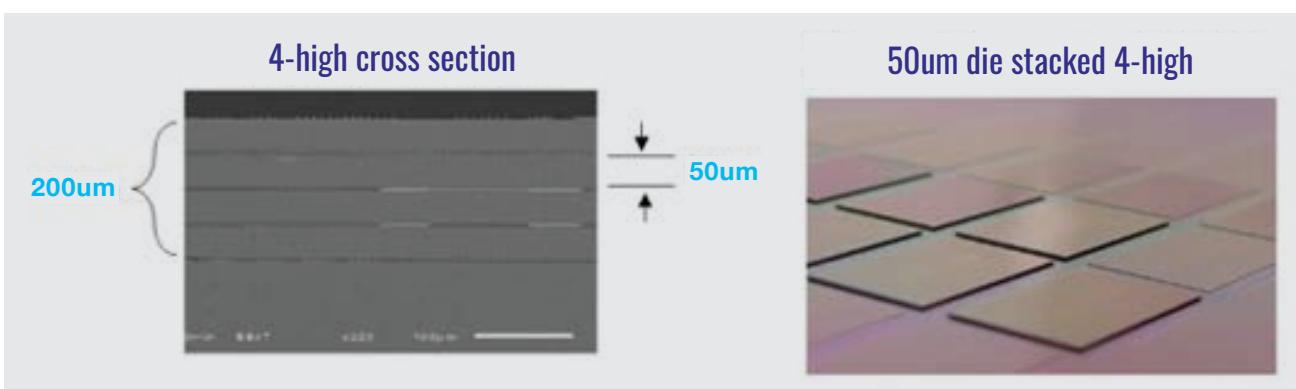

For option two, the chips are stacked and connected vertically. Figure 5 shows the first wave of vertical stacking, which used WB to stack chips on a common base. The second wave stacked package-on-package (PoP) and the 3rd wave, seeking to miniaturize as much as possible, connected die-to-die directly through thinned silicon, resulting in die-to-die interconnect lengths that could be as small as 50 $\mu$ m.

### 3DICs arrive on the scene

The 3rd wave of vertical stacking became known as 3DIC, which, by

Figure 5: Chip packaging goes vertical

| Bonding Method                        | C4 FC (Controlled Collapse Chip Connect) | C2 FC (Chip Connect) | TC/LR (Local Reflow) FC | TC FC   |

|---------------------------------------|------------------------------------------|----------------------|-------------------------|---------|

| Schematic Diagram                     |                                          |                      |                         |         |

| Major Bump Pitch Range at Application | > 130 um                                 | 140 um ~ 60 um       | 80 um ~ 20 um           | < 30 um |

Figure 6: Miniaturization of vertical interconnect.

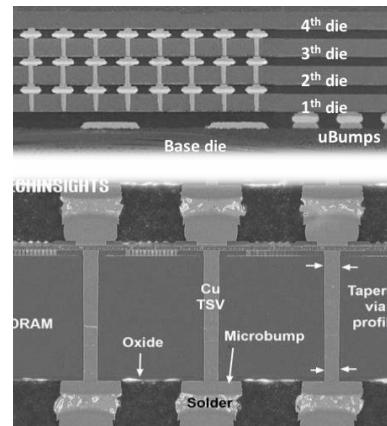

definition, required through silicon vias (TSV), thinning down to 50 $\mu$ m and a die-to-die area array connection technology. As bump connection pitch gets tighter the technology required a move from tin/lead or lead-free solder bumps to so-called copper pillar bumps (CPB), where solder is placed on the tip of a plated copper pillar (Figure 6). For finer pitches, thermo-compression bonding (TCB) must replace mass reflow. At sub 30 $\mu$ m pitch, we will likely need a direct Cu-Cu bonding technology to avoid solder shorting and lower signal degradation.

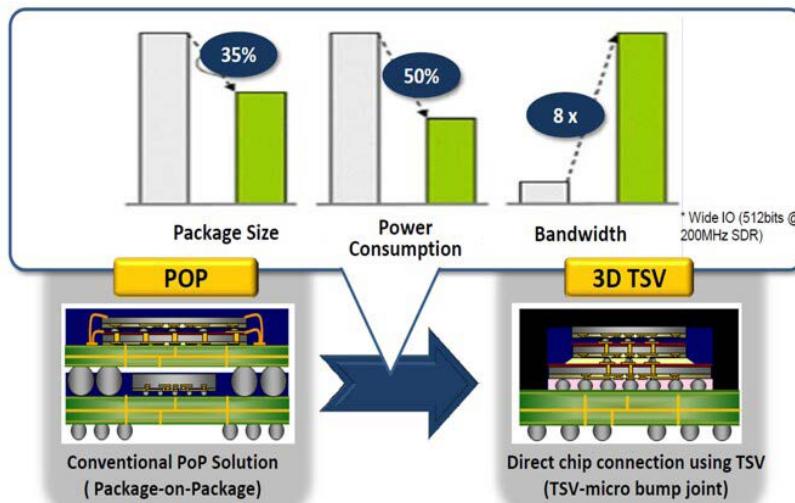

What created high demand for 3DIC were studies, such as one done at Samsung (Figure 7) where identical systems were compared in PoP and 3DIC. The 3DIC solution showed significant size reduction, power savings and 8X increase in bandwidth.

While it was clear that 3DIC resulted in the best possible miniaturization and best possible electrical performance, it required that chip sizes match, and I/O be standardized. It was obvious that it was best

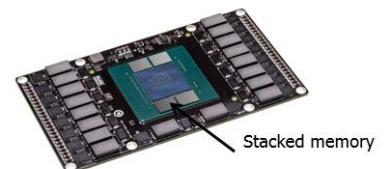

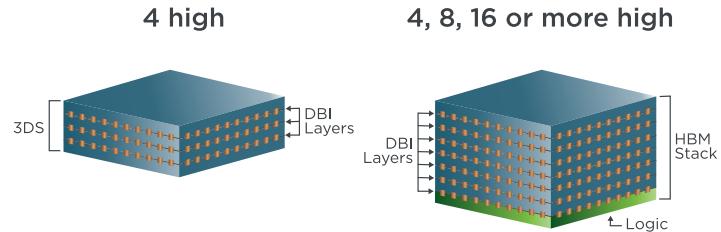

suited for memory stacks where those criteria could be easily met. Hynix and Samsung introduced memory stack products in 2014-2015. High bandwidth memory (HBM) was adopted as an Industry standard by JEDEC in 2013.

While waiting for 3DIC logic, an impatient industry developed “2.5D” technology where a memory stack could be connected on a high density (<1um L/s) silicon interposer to other chip functions. The first such commercial product was developed by Xilinx and TSMC in 2011-2012 where a mega-FPGA was broken up into four segments to increase yields and then reassembled on a high-density silicon interposer.

The graphics module market has also been active in 2.5D with AMD and Nvidia introducing products in 2015-2016 and Intel introducing a high-performance compute module (HPC) in 2015 (Figure 8)

3DIC has also been active in the CMOS Image sensor (CIS) area. In 2008 Toshiba commercialized the first CIS technology using thinned die and backside TSV, but no

Virtex-7 Xilinx (2011)

Knights Landing Intel (2015)

Nvidia Pascal (2015)

AMD Raedon R9 Fury X (2015)

Figure 8: 2.5D product introductions

die-to-die stacking. By 2015 Sony announced the separation of the sensor and the circuitry and in 2017 Sony announced the industry’s first 3-Layer stacked CIS (90nm-generation backside-illuminated CIS top chip, 30nm generation DRAM middle chip, and a 40nm generation image signal processor (ISP) bottom chip).

Most technologists currently agree that 2.5D and 3DIC solutions will be key technologies for future developments in areas such as artificial Intelligence (AI), HPC and robotics, just to name a few.

### The chiplet concept

A new approach to chip design is also making use of 2.5D technology. In the same way that Xilinx broke up their large FPGA into four smaller “chiplets”, which could be subsequently reconnected, large

**Continued on page 60**

**MicroProf® AP** –

Fully Automated

Multi-Sensor Metrology

Tool for Advanced

Packaging.

## METROLOGY FOR ADVANCED PACKAGING

Dedicated solutions for every

process step in one tool!

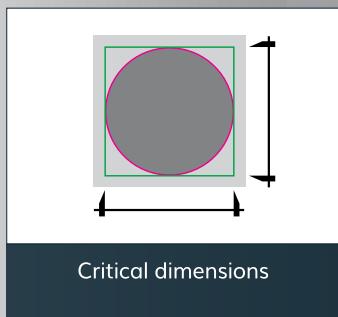

Critical dimensions

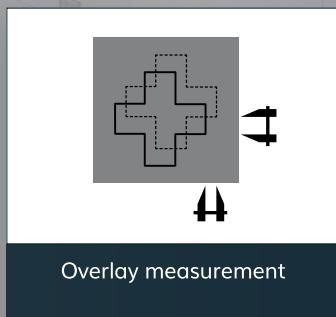

Overlay measurement

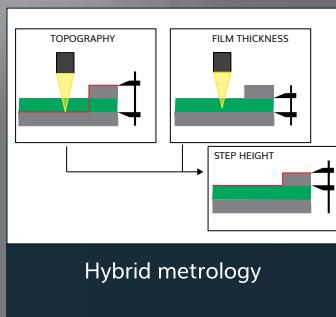

Hybrid metrology

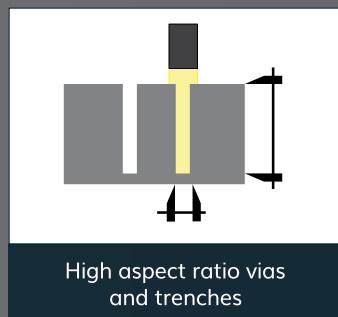

High aspect ratio vias

and trenches

Bump dimensions

and coplanarity

SEMI-compliant thickness

and TTV measurement

Thin film and layer

stack measurement

Defect inspection

Wafer and layer thickness

using IR technology

Bond layer thickness using

IR technology

DIN/ISO-compliant roughness

and waviness measurement

Flatness measurement

More about Advanced Packaging on

[www.frtmetrology.com/en/advancedpackaging/](http://www.frtmetrology.com/en/advancedpackaging/)

# Why Today's Advanced Packages Need Better Inspection

By Fran oise von Trapp

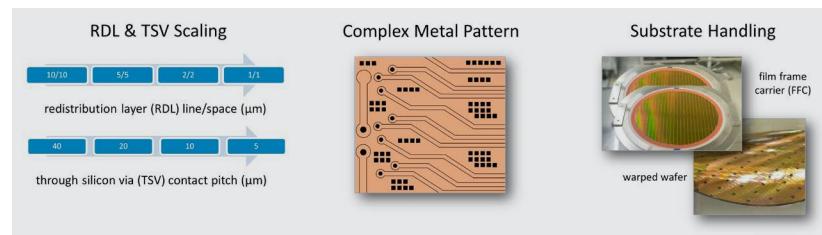

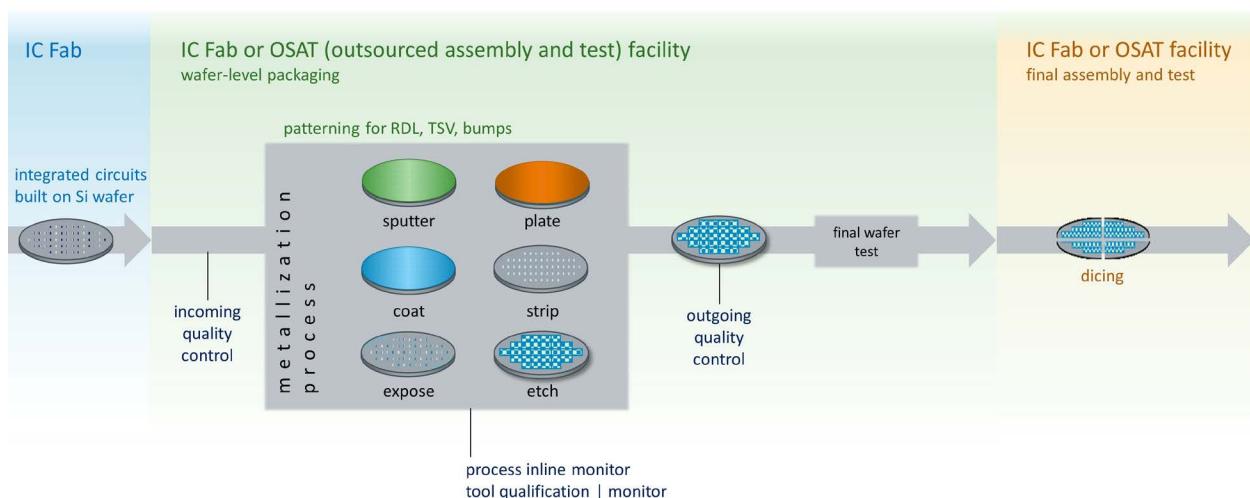

It's almost ironic. As CMOS scaling (aka: Moore's Law) has slowed due to the increased complexity and cost of achieving smaller nodes, the focus has shifted to advanced packaging and heterogeneous integration to meet demands for microelectronics devices targeting the internet of things (IoT) market. These devices perform a variety of functions (sensing, processing, remembering, transmitting) in smaller spaces using less power. Consequently, advanced packages are therefore designed with finer features that require higher density metal patterns, and multi-layer redistribution layers (RDLs).

And suddenly, advanced packages have become as complicated and valuable as the chips they are designed to integrate and protect. With higher value comes a higher concern for improved reliability and yields. As a result, foundries who have expanded their advanced wafer level packaging (AWLP) capabilities and outsourced assembly and test service (OSATS) providers are demanding more sensitive, inspection, metrology, and data analysis—and more accurate identification of bad parts. Not quite the level of inspection used in the front end... but something fairly close.

I interviewed KLA's Lena Nicolaides, Stephen Hiebert, and Pieter Vandewalle to learn about the company's recent developments in metrology and inspection for AWLP and final package inspection, designed to address some defect types that have become more prevalent as advanced packages have become more delicate.

## The role of defect inspection

Defect challenges for WLP include smaller killer defects due to feature sizes, nuisance defects due to complex, dense metal patterns, and high warp wafers and film frame carriers for accommodating

Figure 1: Defect challenges associated with advanced WLP processes, particularly fan-out-wafer-level packaging (FOWLP)

different thickness wafers, as well as reconstituted wafers (Figure 1).

As Hiebert explained it, defect inspection is particularly important during wafer level packaging processes for quality control, process control, and engineering analysis. It helps identify excursions while they can still be reworked and repaired, and again to identify defects that can't be fixed but can cause more problems if they are allowed to

approach to fan-out wafer level packaging (FOWLP), there are typically three layers of RDL and 2-5µm line/space requirements," said Hiebert. "this calls for up to 16 inline inspection steps."

These come at different points throughout the process, the most critical are after the lithography develop step, and again after the etch process in base-metal etch.

Figure 2a: KLA introduced two new inspection solutions targeting advanced WLP

continue through the processes. Through in-line monitoring, causes of defects can be characterized, and the processes tweaked, with the goal of improving final yields.

Additionally, increased package complexity calls for additional inspection steps. "In a chips-first

Defect inspection plays a similar role in test and assembly, although the focus is on outgoing quality control, and not necessarily process control. What's different for the newest wafer level packages, explained Vandewalle, is that previously wafer level packages did not go through the same test and in-

spection as legacy packages, such as lead frame and substrate-based packages. But now, high-end node chips manufactured with low-k materials, which are more brittle and subject to defects (especially after dicing), require advanced inspection, especially to capture chipping, hairline cracks, and laser groove cracks.

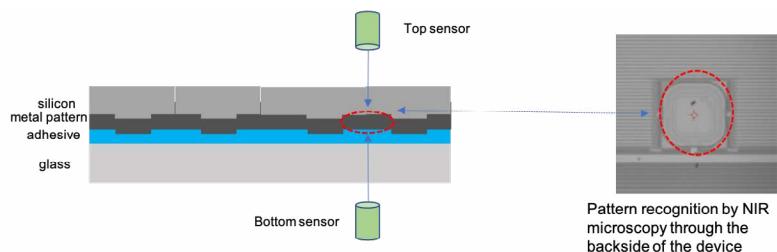

"One reason we decided to pursue this market was that there is no good technology outside of an R&D environment, designed to capture these types of new defects," he explained. "So, we invested in new IR-based technology for the production environment."

### KLA solutions

More than three years in development, KLA recently launched two new systems, the Kronos™ 1080 and the ICOS™ F160, targeting some specific needs of advanced wafer level, 2.5D and 3D integrated packages (Figure 2).

Building on lessons learned with their front-end systems, as well as their existing packaging offerings, CIRCL™-AP, and the ICOS™ line, the company worked in close partnership with its existing customers to identify the gaps in current inspection strategies, and develop these systems, explained Nicolaides

"Our customers who lead in scaling technology came to KLA looking for sensitivity beyond what the

Figure 2b

back-end players could traditionally achieve," she explained. "We designed these systems' architecture and algorithms for a superior cost of ownership, ability to find defects while offering increased throughput and overall yield improvement."

### AWLP process inspection

The Kronos 1080 system is designed to inspect AWLP process steps, providing information on the full range of defect types for inline

process control through multi-mode optics and sensors and advanced defect detection algorithms. Its proprietary FlexPoint™ technology focuses the inspection system on key areas within the die where defects would have the highest impact (Figure 3).

### Final package Inspection

Vandewalle described the challenges in final package inspection that the ICOS F160 is designed to

Figure 3: Kronos 1080 inspects the incoming wafers, performs in-line inspection at specific inflection points when wafers can be reworked, and then is used for outgoing quality control

address, namely low-k cracks on sidewall and laser grooves that are difficult to detect. The system's purpose is to be used in high-volume manufacturing to separate out the bad parts and keep the good.

In designing the ICOS F160, Vandewalle said the focus was finding a solution to address dicing cracks caused by an aggressive dicing practice. Existing approaches relied on either optical or open/short tests, but none was good enough to capture critical defects. He said that as a result, the packages fail in the end-use device, and mobile and wearable companies are suffering from the slip-through.

The ICOS F160 features IR inspection, which provides robust detection of invisible killer crack defects for fan-in WLP, memory and bare die. In combination with 6-side optical inspection with pre- and post-placement inspection, the ICOS F160 enables high die sorting accuracy. Additionally, the system's flexibility allows it to support a variety of workflows, including wafer-to-tape and tape-to-tape. Lastly, fast conversions, automatic calibration, and precision die pickup addresses the needs of high-volume manufacturing (Figure 4).

#### Where the action is

While CMOS scaling may continue, advanced WLP is clearly where the action is, driven by the IoT explo-

Figure 4: ICOS F160 key technologies to address high volume die sort challenge.

sion. Because advanced packaging technologies are so much more varied than front-end processes, the greatest challenge for KLA was developing systems next-generation inspection systems that are both flexible and high-performing.

"There's always a trade-off. The more flexible you make something, the more challenging it is to achieve optimized performance,"

said Nicolaides. "After analyzing the requirements of the diverse package designs, we focused on defect sensitivity and inflection points to leverage our optical expertise."

The result of that focus has been realized in the addition of these two systems to their product portfolio.

~ FvT

# Diversification of Markets Calls for Hybrid Metrology with Multi-Sensor Technology

By Françoise von Trapp

People used to think about metrology for front-end process control and inspection in semiconductor manufacturing only. As wafer level packaging (WLP) and heterogeneous integration (HI) approaches became more advanced, metrology processes began creeping into back-end process control, where measurement becomes trickier and more diversified. I spoke with Thomas Fries, CEO of FRT, winner of the 2018 3D InCites Equipment Supplier of the Year Award. We talked about how technology diversification is here to stay, and how hybrid metrology solutions using multi-sensor technology are becoming necessary.

## Metrology for Advanced Packaging

"For the past two years, we've had a strong demand for tools that perform different metrology tasks," noted Fries. "Inspection used to be the standard, but now metrology is becoming a must-have." He went on to explain the impact the lack of mainstream processes is having on metrology solutions providers.

Despite continued efforts to scale CMOS structures to smaller nodes, metrology needs are fairly straightforward thanks to standardization of tools and processes. This is not the situation for metrology in the advanced packaging space. Measuring total thickness variation (TTV) on a wafer is not the same as measuring TTV with a very high lateral resolution. Additionally, through silicon vias (TSVs), Cu bump or pillar heights, as well as thinning, bonding and stacking are bringing new metrology needs compared to classical process steps.

## Diversity changes everything

The dawn of fan-out (FO) processes both at the wafer and panel level has added more diversity to metrology needs. Add to that 2.5D and 3D heterogeneous integration, and now chiplet technologies and the diversity of the space continues to broaden. This is not the volume-driven market tier-one

Figure 1: Thomas Fries, CEO FRT, accepts the 3DInCites Award outside the FRT cleanroom

metrology tool providers are used to serving.

"With MicroProf® AP, we succeed to accommodate measurement requirements for different processes, and we are able to handle both wafers and panels, thinned and bonded wafers, and film frames," noted Fries.

Additionally, he says he doesn't expect the players to settle on one approach for all, because different applications call for different device architectures, which in turn require different processes. He does, however, expect a narrowing of options.

"For FRT this is a fantastic situation," said Fries. "Our early decision to focus on building tools with multiple sensors and to program our own software in-house is paying off. We are perfectly set up for doing hybrid metrology with multi-sensor technology, which is what is needed for these complex processes."

## The hybrid metrology solution

So what exactly is hybrid metrology? Fries explains that for FRT, it means using its multi-sensor concept so that in one recipe, different properties on a device can be automatically measured. Up to ten fully integrated sensors act as one to automatically embed different information and create new information that isn't directly available.

Fries explained further: In the same tool, you can now, for example, measure the height of a Cu bump against the oxide in silicon in the same machine. The step height of the Cu is measured optically, and a film thickness sensor is used to measure oxide thickness. By subtraction, the film thickness, the height of the Cu above the oxide can be determined.

Additionally, with the company's third generation of tools, the up-to-date, in-house developed software, achieves 64-bit status.

## MicroProf® AP

AP, designed for advanced packaging. It allows fully automated processing of 300mm FOUPS/FOSBs and 300 mm/200 mm/150mm open cassettes. The system can handle SEMI standard wafers, highly warped wafers (e.g. eWLB), bonded wafers, wafers on tape, TAIKO, bare and thinned wafers, and even fan-out wafers. Moreover, the tool can be configured for processing frame cassettes and handling of panels. The handling part features a robot with end-effector, two load ports including mapper and RFID reader, pre-aligner and optional OCR reader stations. It can be used for all metrology tasks within the advanced packaging process, e.g. measurement of photo resist (PR) coatings and structuring, through silicon vias (TSVs) or trenches after etching,  $\mu$ -bumps and Cu pillars, as well as for the measurement in thinning, bonding and stacking processes.

As standard configuration, the MicroProf® AP is equipped with a granite base setup, with a three- point sample fixture or a vacuum chuck. Besides that, numerous features can be added or retrofitted on site at a later time.

RT practices the Art of Metrology

This so-called hybrid metrology tool is the perfect fit for diversified markets, says Fries. "It paradoxically solves what the customer wants: a standard tool that can follow an established roadmap with on-site upgrades and can also handle diverse process steps and the ability to customize solutions," he said.

### Serving niche markets

Fries firmly believes that the key to success does not lie in trying to be all things to all people. With this in mind, his strategy is to focus on three growing specific markets: advanced packaging, MEMS, and LED applications.

"The market is interesting and gives us lots of options. But it's important that we focus on niche markets and not try to do everything," he said. "The newest, hottest applications call for new processes and metrology tools and have to be flexible to adapt to new process quickly. This isn't what the tier-one suppliers focus on. They aren't keen on serving niche markets because the low volumes don't make it worthwhile."

As a result, he says the competitive overlap is diminishing. "We don't meet most of those competitors in the market anymore," notes Fries. "There's room for all of us to succeed."

### The best of both worlds

What Fries likes best about FRT is having the flexibility and capability to serve both niche and high-volume markets. The company's hybrid metrology and inspection solutions suit the current climate of application diversity perfectly.

Usually, a company decides to pursue tier-one or niche customers. This is not the case for FRT. Even though they focus on serving the niche markets, their toolbox allows them to support both, combining the best of both worlds.

## Measure the Immeasurable

of various measurement tasks using different sensors to run consecutively within a measurement sequence is simplified. Add to that, this software provides comprehensive capabilities, from manual measurement on the device to fully automated measurement with one button operation and integration into production control systems, e.g. via a SECS/GEM interface.

By the magic of FRT's software developed in-house, it is possible to measure things that previously couldn't be measured. The configuration

By using a hybrid metrology concept - this multi-sensor metrology tool enhances the precision of measurements on samples where a single sensor or measuring principle is just not enough. Depending on the task, this may include measurements with different topography and (film) thickness sensors that are fully automated by a single recipe.

# 3D Test: No Longer a Bottleneck!

By Erik Jan Marinissen – imec, Leuven (Belgium)

When I joined imec in October 2008 to work on test and design-for-test (DfT) of 3D-stacked integrated circuits (ICs), there were only a few test folks active in that emerging field. Consequently, misconceptions about 3D test were omnipresent. In the November 18, 2008 issue of Semiconductor International, Alexander Braun wrote: “At a symposium yesterday on 3-D integration, leading expert Philip Garrou detailed the rise of the technology as well as the challenges facing it, including test, yield, and design. (...) Test, again, will be a significant problem. Memory can be stacked as known good die, because the memory chips can be tested, but years from now, as different functions are pulled apart to stack them, there is no clear way to test them because they do not form a complete circuit. This will hold up things like the full partitioning of chips.”<sup>1</sup> 3D InCites’ tenth anniversary is a good occasion to report on the state of 3D testing and publicly declare that it’s no longer a bottleneck for 3D integration.

## Structural Modular Test

‘Test’ is an overloaded term. While some people might think of design verification (on a simulation model) or design validation (on the real chip), this article is restricted to electrical testing for manufacturing defects, typically in a high-volume setting. At this stage of product development, we assume chip designs are correct. Chip manufacturing processes are defect prone as they consist of large numbers of high-precision steps. Unavoidably things go wrong every now and then, leading to spot defects such as shorts and opens.

For a large chip manufactured using advanced technology, the die yield might be 80%, while customers typically tolerate defective chips in quantities of no more than 100 defective parts per million (dppm). Consequently, a test needs to be a very effective filter for defective chips. Because every transistor or interconnect segment on a chip can suffer from defects, each chip

needs to be tested, and hence the test needs to be very efficient; taking no more than a few seconds per chip in a fully automated process.

During test, stimuli are fed into the chip and corresponding responses on the chip outputs are compared to expected responses to determine ‘pass’ or ‘fail’. Automatic test pattern generation (ATPG) tools, available from all major EDA suppliers, try to cover as many potential fault locations as possible with a minimum of test patterns to reduce test time and associated cost.

ATPG tools do not utilize application knowledge of the device-under-test (DUT), but instead base themselves on the DUT’s structure: the gate-level netlist with interconnected library-cell instances (AND, OR, flip-flop, etc.). The resulting test patterns have no relation with the mission-mode (‘functional’) operation of the chip, but check if these cells are

present, operational, and correctly interconnected. We refer to this as a structural test (as opposed to a functional test).

For a structural test, testing a single die that only implements a partial function of a multi-die stack is no problem at all. This modular approach to test development and execution has become common practice in the industry.

Today’s core-based system-on-chips (SOCs) are routinely tested in a modular fashion: core-by-core, sequentially, or at the same time.<sup>2</sup> For 3D integrated circuits (3D ICs), for which the various stacked dies might be designed and/or manufactured by different parties, modular testing (here: die-by-die) makes even more sense. The benefits include:

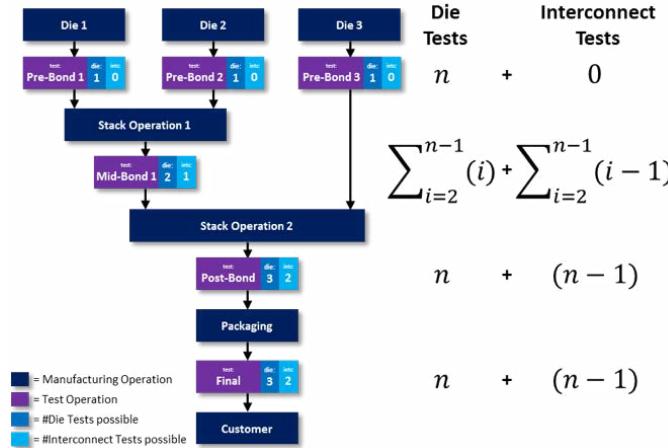

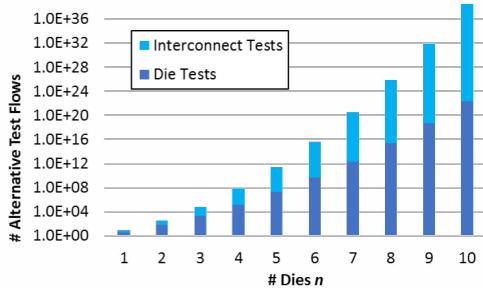

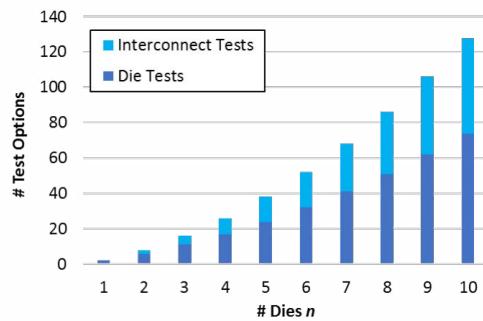

Figure 1a: Example test flow for  $n=3$ : maximal 11 die tests and 5 interconnect tests. Figure 1b: Equations for  $t(n)$  as function of the number of dies in the stack  $n$ . Figure 1c: Number of test  $t(n)$ , for increasing number of stacked dies  $n$ . Figure 1d: Number of alternative test flows  $f(n)$ , for increasing number of stacked dies  $n$ .

- Targeted test pattern generation, tailored to the circuit type (e.g., logic or memory) and function, preferably by the team also responsible for the design

- Freedom to (re-)schedule the various die tests if manufacturing yields so require (test engineers like to put tests that are more likely to fail early in their test suite, to reduce the per-die average test time by applying 'abort-on-fail')

- Re-use of tests in case design modules are reused

- First-order fault diagnosis and yield attribution (because: if the test for a particular module fails, that module most likely contains the root cause)

### Test Flow Optimization

A major difference between testing 2D and 3D ICs is the potential complexity of the test flow. At which moments in the manufacturing flow do we execute a test for what stack component? Conventional 2D chips typically have two test moments: first while still in their wafer (wafer test, a.k.a. e-sort), to avoid package costs for defective dies, and then again after assembly and packaging (final test), to guarantee the outgoing product quality toward the customer. 3D ICs have many more test moments, tests, and hence test flows. For an  $n$ -die stack, we have prior to stack assembly  $n$  possible test moments during which we can execute a pre-bond test on a die. After every stack assembly operation, we have a new test moment, in which each die and interconnect layer in the stack built up so far can be tested. We refer to these test moments as mid-bond tests (for partial stacks) and post-bond tests (for complete stacks). There are  $\sum_{i=2}^n (i)$  die tests and  $\sum_{i=2}^n (i-1)$  interconnect tests possible during these test moments. After packaging, the final test can contain  $n$ -die tests and  $(n-1)$  interconnect tests. In total, an  $n$ -die stack has  $2n$  test moments during which a grand total of  $2n-1 + \sum_{i=2}^n (i)$  die tests and  $n-1 + \sum_{i=2}^n (i-1)$  interconnect tests might occur. In practice, there might be no physical test access during certain test moments, which

reduces the number of feasible tests. A test flow consists of an execution decision (yes/no) for each test at each feasible test moment. If a die stack has a total of  $t(n)$  tests, this allows for  $f(n) = 2^{t(n)}$  alternative test flows. Note: this definition of  $f(n)$  does not account for alternative test schedules due to reordering of tests at a particular test moment.

Figure 1(a) illustrates the test flows for a relatively simple stack with only three dies, resulting in 16 tests (11 die + 5 interconnect tests), and therefore a total of  $216 = 65,536$  alternative test flows.

In practice, some test moments might not permit probe access, and this reduces the number of feasible tests and test flows. For example, for imec's FC-FOWLP test chip consisting of seven dies, from the theoretical 68 tests only 33 tests are practically feasible; which still implies a whopping  $233 \approx 8.6 \times 10^9$  alternative test flows.

Figure 1(b) shows the generic equations for  $t(n)$  as function of the number of stacked dies  $n$ . Figures 1(c) and 1(d) depict  $t(n)$  respectively

$f(n)$  as function of the number  $n$  of stacked dies.<sup>3</sup>

The large numbers of alternative test flows necessitate computer support. The 3D-COSTAR software tool, developed by TU Delft and imec, makes a cost analysis of a user-specified manufacturing and test flow.<sup>4</sup> The tool considers costs proper to design, as well as five manufacturing operations:

1. Wafer processing

2. Stack assembly

3. Test

4. Packaging

5. Logistics

These operations are considered not perfect and are modeled with an associated yield in percent. For test, 'yield' is defined as 100% minus the test escape rate (in dppm). 3D-COSTAR calculates the lump-sum costs per operation, where all costs are attributed to those stacks that pass the entire flow and are shipped to the customer. The tool can analyze the effect of varying

From the analytical lab to the production fab.

Learn more at [www.formfactor.com](http://www.formfactor.com)

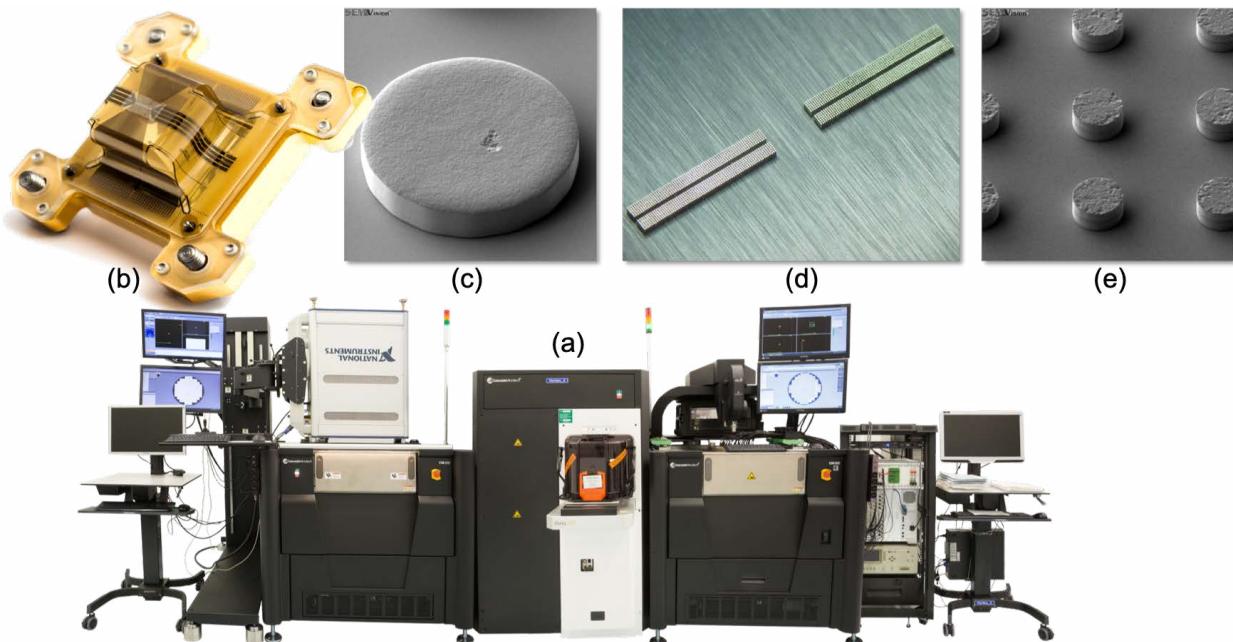

Figure 2: 'Vortex-2' test system in imec's Fab-2, based on FormFactor's CM300 probe station (a), has been used for probing large-array 40 $\mu$ m-pitch pbumps with advanced probe cards. FormFactor's Pyramid® RBI probe cards (b) left small probe marks on 0.25 $\mu$ m Cu pbumps (c), and Technoprobe's TPEG™ T40 probe cards (d) left barely visible probe marks on 0.15 $\mu$ m Cu/Ni/Sn pbumps (e).

an arbitrary number of parameters (in lock-step) along one or two independent axes, as variations of a user-defined base case. The output of the analyses is an estimation of product quality (defective chips that nevertheless pass the test, in dppm) and the cost per shipped stack, sub-divided over the subsequent manufacturing operations.

### Test Access

The main challenges of 3D testing are related to test access: delivering test stimuli to where they can detect the presence of a defect, and the test responses in the opposite direction. Test access comprises two components: external test access, i.e., from the test equipment to the chip I/Os and back, and internal test access, i.e., from the chip inputs to the actual on-die defect location and back to the chip outputs.

With external test access, several challenges and their solutions related to probing on 'naked' (= not-yet-packaged) dies or die stacks are described below. Internal test access is handled by on-chip DfT hardware. The conventional ('2D') DfT has been extended with 3D-specific features, and those are described at the end of this article.

### Probing Challenges and Solutions

For most product scenarios, realistic yields require a combination of pre-bond, mid-bond, and post-bond testing. This prevents manufacturing defects from being discovered too late in the stack-assembly flow thus requiring the entire stack to be scrapped, including perhaps other (defect-free) dies. Whereas test access contact for final test is made through a test socket, the pre-, mid-, and post-bond tests all depend on probe technology. For multi-die stacks, the following probing challenges have been identified and resolved in collaboration with our partners.<sup>5</sup>

#### Probing on large tape frames.

Stack-assembly flows for multi-die stacks frequently use tape frames as a temporary carrier: for diced wafers, for aggressively thinned-down wafers, for pick-n-placed dies and die stacks, etc.<sup>6</sup> Out of necessity, a tape frame is larger than the wafer it holds; for a 0.300mm wafer, the outer dimension of the frame is 0.400mm.<sup>7</sup>

Imec worked with Cascade Microtech (now FormFactor) to specify and implement adaptations to the CM300 probe station, so that 0.300mm wafers on a large tape

frame can be loaded manually.<sup>6</sup> The Tokyo Electron WDF™-12DP probe stations even have an automatic loader for such large tape frames.<sup>8</sup>

#### Probing ultra-thin wafers on a flexible tape.

Wafer thinning is commonly performed on dies used in multi-die stacks: from 780 $\mu$ m down to ~200 $\mu$ m to fit the stacked dies into a standard-height package cavity or, when TSVs are employed, even thinner to expose the TSVs at the wafer back-side (at imec: 50 $\mu$ m). Stretched UV-curable dicing tape, laminated over a tape frame, is commonly used as a temporary carrier to prevent ultra-thin wafers from sagging and curling.

The forces exercised by probe needles should be sufficiently high to guarantee an acceptable low contact resistance between each probe tip and its corresponding probe pad. However, when we do this on an ultra-thin and flexible wafer atop flexible dicing tape, we should avoid probe forces that cause permanent or even temporary stress-induced electrical or mechanical effects and damage.

At imec, we have done numerous experiments with probe cards that require different probe forces: conventional cantilever, FormFactor's

Pyramid® and Pyramid® RBI (Rocking Beam Interposer) MEMS-type probe cards, and Technoprobe's ARIANNE™ and TPEG™ probe cards. We recommend a low-force probe card in this situation.

### Probing large arrays of fine-pitch micro-bumps.

The interconnect between stacked dies consists of large arrays (>1,000) of Cu and Sn micro-bumps at ultra-fine pitch: 40µm. Imec has developed a unique test system to characterize probe cards that claim to be capable of probing such micro-bump arrays. It consists of a FormFactor CM300 probe station with hard-docking National Instruments test head with 1,216 parametric tester channels.<sup>9</sup>

Imec has in-house manufactured test wafers with only micro-bumps (>10 million micro-bumps at 40µm pitch on a ø300mm wafer) in various metallurgies. This set-up has been successfully used to characterize advanced micro-bump probe cards which imec co-developed with leading suppliers: FormFactor's Pyramid® RBI and Technoprobe's TPEG™ T40.<sup>10, 11</sup>

### Probing singulated dies and die stacks on a flexible tape.

The challenge is that the probe targets might have translated or rotated from their original wafer-map position, such that blind index stepping by the probe station is no longer possible. This happens when probing on diced wafers or diced stacks on dicing tape, due to the flex-n-stretch forces of the dicing tape).

Another application is pick-and-place of die-to-die stacks on a carrier substrate, as the pick-and-place tool might be insufficiently accurate for subsequent probing.<sup>8</sup> Together with our partner FormFactor, we have developed and successfully demonstrated software that determines the individual misalignment per die or die stack at the start of the wafer probe session and then compensates for it while probing.<sup>8</sup>

Originally deemed impossible when we started to work on this topic in 2011, today imec is probing 40µm-pitch micro-bump arrays on a rou-

tine basis. Recently, we reported on a case study where all probing challenges described above and their proposed solutions, were applied in a combined fashion.<sup>5</sup>

### 3D-Design-for-Test Architecture

For transportation of stimuli and responses within the die (stack), we need on-chip DfT. Conventional 2D-DfT includes internal scan chains, test data compression to handle large dies, core-test wrappers around embedded cores and other design units that will be tested as stand-alone units, and built-in self-test hardware for embedded memories. The term '3D-DfT' refers to on-chip DfT features that are explicitly added to handle 3D ICs.

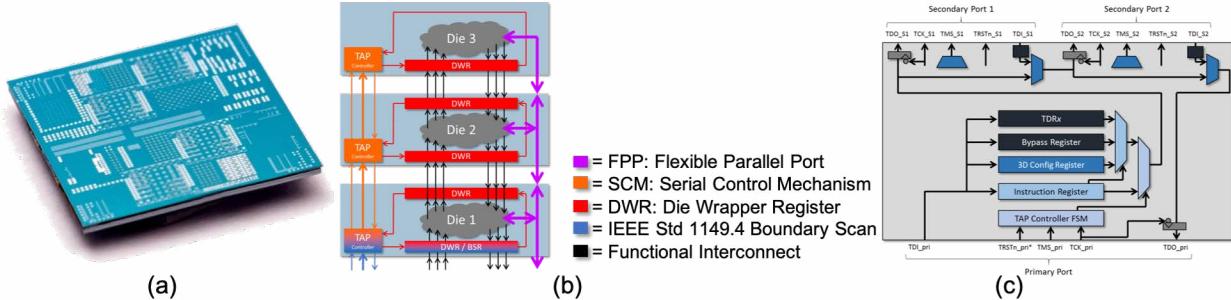

A 3D-DfT architecture should support a per-die modular test approach and therefore requires wrappers at die level, such that the various dies and their inter-die interconnects can be tested independently from each other. Whereas conventional 2D core wrappers (as specified by IEEE Std 1500<sup>12</sup>) have one test input and one test output port, a 3D-DfT die wrapper should support multiple test ports.

A die has its test data to and from the test equipment enter and exit via its primary test port. In case one or multiple other dies are stacked directly on this die, it will also have a corresponding number of secondary test ports, which each serve as a plug for the primary test ports of one of these stacked dies. In this way, test stimuli can enter the stack through the primary test port of the base die, be transported up in the stack, possibly through other dies, to reach the destination die where they execute their defect detection work; likewise, test responses need to be transported from the DUT through other dies in the stack down to the external stack I/Os.

Imec defined and patented a 3D-DfT architecture that meets these requirements, initially for single-tower logic-on-logic die stacks (Figure 3). With Cadence Design Systems we developed EDA tool flows for DfT insertion and test generation; and we designed, manufactured (partly at GlobalFoundries,

partly at imec), and tested successfully a demonstrator IC containing the proposed 3D-DfT.<sup>13, 14</sup>

The EDA tool flows were made available as a rapid adoption kit (RAK) to Cadence customers, used for several TSMC test chips, and released as TSMC Reference Flow for CoWoS and 3D-IC. We extended the basic architecture with provisions for memory-on-logic stacks; logic dies to be complex SOCs with a hierarchical design and test approach, containing embedded IP cores and test data compression; for multi-tower stacks to support at-speed test of the inter-die interconnects; and to create realistic test conditions by controlling the switching activity of dies and cores neighboring to the current module-under-test.<sup>15, 16, 17, 18</sup>

### 3D-DfT Standardized: IEEE Std P1838

To guarantee interoperability of the 3D-DfT architecture across the various dies in a stack, especially if these dies are designed by different teams or companies, a standardization effort was needed. This was done under the umbrella of IEEE Standards Association, as other DfT standards reside there as well.

In 2011, I founded a standardization working group under IEEE sequence number P1838. Standardization is intrinsically a slow process, but after eight years, the draft standard is finally nearing completion. At the end of 2018, the ballot group has been formed and in 2019 the actual ballot will take place, hopefully leading to an approved standard still in the same year. IEEE Std P1838 standardizes per-die 3D-DfT features, such that compliant dies are brought together in a die stack, a basic minimum of cooperative test access is guaranteed to work across the stack.<sup>19</sup>

IEEE Std P1838 consists of three main components: a die wrapper register (DWR), a serial control mechanism (SCM), and a flexible parallel port (FPP). DWR and SCM are 3D extensions of existing standards IEEE Std 1500 and IEEE Std 1149.1, respectively. The FPP, a novel feature of P1838, is an optional, scalable multi-bit ('parallel')

Figure 3: 'Vesuvius-3D' two-die stack containing a 3D-DfT demonstrator<sup>14</sup> (a), overview of the IEEE Std P1838 3D-DfT architecture (b), and detail view of P1838's serial control mechanism on a single die with two secondary ports (c)<sup>19</sup>.

test access mechanism that offers higher bandwidth compared to the one-bit ('serial') mandatory part of P1838.<sup>20</sup>

## Conclusion

DfT and test engineers know the limits of their work. Our industry is not making chips because the test community has developed a fancy test solution for them; customers would not care. They are interested in more performance, more storage capacity, and higher bandwidth, benefits which can be achieved with 3D ICs. But, on the other hand, our industry cannot put high

volumes of products with wonderful new performance/storage/bandwidth features on the market, if these products are not individually tested for defects. Customers do not accept that.

The mere fact that the test community started working on 3D ICs was a clear sign that release of actual 3D products was imminent. With the solutions described in this article, most of the test challenges related to 3D ICs have been addressed, such that we can conclude that 'test' is no longer a bottleneck for market introduction of 3D ICs. The test community has

delivered, adequately and, while the first products are hitting the market, just on time!

If you want to read more about 3D (test) challenges and solutions: they are described in detail in the book "Design, Test, and Thermal Management", edited by Paul D. Franzon (NCSU), Erik Jan Marinissen (imec), and Muhamad S. Bakir (Georgia Institute of Technology).

This book is Volume 4 in the well-known book series "Handbook of 3D Integration", published by Wiley-VCH and available from March 2019 onward.

# WDF™ 12DP+

## 300mm wafer dicing frame prober

[www.tel.com](http://www.tel.com)

## Features

- Fully automatic dicing frame and standard wafer handling

- Change Over KIT to easily switch between 300mm and 200mm

- "N-Shot" alignment for high accuracy, parallelism probing for diced wafer

- Improved system cleanliness and ESD\*

- TEL standard prober application software "PSAS"

## Applications

- Post dicing test for KGD\*, RMA\*

- Advanced package test capability (WLP, FOWLP, panel level package)

- Test for thin wafer, multiple PCB, strip frames on dicing frames

\*ESD: Electro Static Discharge

\*KGD: Known Good Die

\*RMA: Return Merchandise Authorization

TEL is a registered trademark or trademark of Tokyo Electron Limited in Japan and/or other countries.

## About the Author

Erik Jan Marinissen is principal scientist at imec in Leuven, Belgium, the world-leading independent R&D center in nanoelectronics technology. His research on IC test and design-for-test covers topics as diverse as 3D-stacked ICs, CMOS below 10nm, silicon photonics, and STT-MRAMs. Marinissen is also visiting researcher at Eindhoven University of Technology in the Netherlands. Previously, Marinissen worked at NXP Semiconductors and Philips Research in Eindhoven, Nijmegen, and Sunnyvale.

Marinissen is (co-)author of 250+ journal and conference papers (h-index: 43) and (co-)inventor of 18 patent families. He has received numerous awards for his work and is very involved in IEEE conferences and standards. Among them, he served as editor-in-chief of IEEE Std 1500 and as founder/chair (currently vice-chair) of the IEEE Std P1838 Working Group on 3D-SiC test access.

## Acknowledgments

I thank many colleagues and partners for their fruitful cooperation: Alkis Hatzopoulos, Leonidas Katselas (Aristotle Univ. of Thessaloniki), Teresa McLaurin (Arm), Vivek Chickermane, Brion Keller, Christos Papameletis (Cadence Design Systems), Tobias Burgherr (FHNW), Eric Hill, Jörg Kiesewetter, Ken Smith (FormFactor), Sandeep Bhatia (Google), Pieter Bex, Eric Beyne, Bart De Wachter, Ferenc Fodor, Mario Konijnenburg, Arnita Podpod, Michele Stucchi (imec), Yu Li, Ming Shao (KU Leuven), Chun-Chuan Chi (NTHU), Adam Cron (Synopsys),

Daniele Acconcia, Raffaele Val-lauri (Technoprobe), Paul Mooney, Eric Pradel, Yoichi Shimizu (Tokyo Electron), Sandeep K. Goel (TSMC), Sergej Deutsch (TU Braunschweig), Said Hamdioui, Motta Taouil, Jouke Verbree (TU Delft), Hailong Jiao (TU Eindhoven), Konstantin Shibin (TU Tallinn), and Michael Wahl (Univ. Siegen).

Part of this work was performed in the project ESiP, 'Efficient Silicon Multi-Chip System-in-Package Integration – Reliability, Failure Analysis and Test', funded by the ENIAC Joint Undertaking (<http://www.eniac.eu>). This project was winner of the ENIAC Innovation Award 2013. Part of this work was performed in the project SEA4KET, 'Semiconductor Equipment Assessment for Key-Enabling Technologies' (<http://www.sea4ket.eu>), sub-project 3DIMS, 3D Integrated Measurement System, which received funding from the European Union's Seventh Programme for research, technological development, and demonstration under grant agreement No. IST-611332.

## Awards Related to This Work

Erik Jan Marinissen received the Meritorious Service Award from the Test Technology Technical Council of IEEE Computer Society "for significant services as Program Chair of the IEEE International Workshop on Testing Three-Dimensional Stacked ICs (3D-TEST) since 2010".

Mottaqiallah Taouil, Said Hamdioui, and Erik Jan Marinissen received the Technology Transfer Award 2015 from HiPEAC for the 3D-COSTAR Test Flow Optimization Tool (<https://www.hipeac.net/news/6774/hipeac-tech-transfer-award-2015-winners-announced/>).

Imec received the Research Institute of the Year 2017 award from 3DInCites (<https://www.3dincites.com/3d-incites-awards/2017-3d-incites-awards-winners/>).

Ferenc Fodor, Bart De Wachter, Erik Jan Marinissen, Jörg Kiesewetter, and Ken Smith received the Engineering Impact Award 2017 from National Instruments in the category Electronics and Semiconductors for large-array

fine-pitch micro-bump probing (<https://forums.ni.com/t5/NI-Blog/Changing-the-World-with-Science-and-Engineering-2017-Engineering/ba-p/3615313>).

Erik Jan Marinissen received the Emerging Technology Award 2017 from the IEEE Standards Association "for his passion and initiative supporting the creation of a 3D Test Standard" (<https://standards.ieee.org/about/awards/etech>).

## References

1. Alexander Braun, '3-D Integration Lacking in Design and Test Support', Semiconductor International, November 18, 2008

2. Erik Jan Marinissen and Yervant Zorian, 'IEEE 1500 Enables Modular SOC Testing', IEEE Design & Test of Computers, Special Issue on 'IEEE Std 1500 and Its Usage', Volume 26, No. 1 (January/February 2009), pp. 8-17, DOI 10.1109/MDT.2009.12

3. Arnita Podpod, Dimitrios Velenis, Alain Phommahayxay, Pieter Bex, Ferenc Fodor, Erik Jan Marinissen, Kenneth Juno Rebibis, Andy Miller, Gerald Beyer, and Eric Beyne, 'High Density and High Bandwidth Chip-to-Chip Connections with 20µm Pitch Flip-Chip on Fan-Out Wafer Level Package', Innl. Wafer-Level Packaging Conference (IWLPC'18), San Jose, CA, USA, October 2018, DOI 10.23919/IWLPC.2018.8573262

4. Mottaqiallah Taouil, Said Hamdioui, Erik Jan Marinissen, Sudipta Bhawmik, 'Using 3D-COSTAR for 2.5D Test Cost Optimization', IEEE International 3D Systems Integration Conference (3DIC'13), San Francisco, CA, USA, October 2013, pp 1-8, DOI 10.1109/3DIC.2013.6702351

5. Erik Jan Marinissen, Ferenc Fodor, Arnita Podpod, Michele Stucchi, Yu-Rong Jian, and Cheng-Wen Wu, 'Solutions to Multiple Probing Challenges for Test Access to Multi-Die Stacked Integrated Circuits', IEEE International Test Conference (ITC'18), Phoenix, AZ, USA, October 2018

6. Erik Jan Marinissen, Bart De Wachter, Teng Wang, Jens Fiedler, Jörg Kiesewetter, and Karsten Stoll, 'Automated Testing of Bare Die-to-Die Stacks', IEEE International Test Conference (ITC'15), Anaheim, CA, USA, October 2015, Paper 20.2, DOI 10.1109/TEST.2015.7342412

7. SEMI G74-0669 Specification for Tape Frame for 300mm Wafers. Semiconductor Equipment and Materials International, San Jose, CA, USA, May 1999

8. Tokyo Electron Notification, 'Tokyo Electron (TEL) Introduces a Dual Purpose 300mm Dicing Frame Prober', November 2008 (see [http://www.tel.com/news/top-ics/2008/20081104\\_001.html](http://www.tel.com/news/top-ics/2008/20081104_001.html))

9. Erik Jan Marinissen Ferenc Fodor, Bart De Wachter, Jörg Kiesewetter, Eric Hill, and Ken Smith, 'A Fully Automatic Test System for Characterizing Large-Array Fine-Pitch Micro-Bump Probe Cards'. In Proc. IEEE International Test Conference Asia (ITC-ASIA), September 2017, DOI 10.1109/ITC-ASIA.2017.8097130

10. Erik Jan Marinissen, Ferenc Fodor, Bart De Wachter, Jörg Kiesewetter, Ken Smith, and Eric Hill, 'Evaluation of Advanced Probe Cards for Large-Array Fine-Pitch Micro-Bumps', Chip Scale Review magazine, Volume 21, No. 1

**Continued on page 60**

# Special Section: The Past, Present and Future of 3D Integration

On this, the occasion of the 10th Anniversary of 3D InCites, we asked our advisory board and other members of the industry to reflect on the past 10 years of the 3D integration journey, and answer two questions:

**1** What was the single most pivotal event (good or bad) in the last 10 years that impacted the commercialization of 3D integration technologies?

**2** Looking into your crystal ball, where will 3D and heterogeneous integration technologies take us in the next 10 years?

The responses we received ranged from insightful comments and personal reflections, to longer editorial contributions and analyses, both market and technical. Every contribution offered insight and perspective, so we chose to create this special section featuring them all. Enjoy!

## 3D InCites Turns 10: A Brief Analysis of the 3D Journey

By Yann Guillou, Trymax

I cannot believe 3D InCites is already turning 10! As wise people

say, time flies! Taking a step back, I have to admit a lot of progress has been made since my first attendance as a young engineer to the EMC 3D workshops back in 2008. At that time, we were discussing how to form a via, how to fill it, how to use a temporary wafer carrier to process thin wafers...etc.

We are definitely more mature now (not old!) and I'm convinced 3D InCites contributed to the progress by sharing knowledge across the industry.

I'm honored to have been part of their advisory board since 2010 under the enthusiastic leadership of Françoise. Following is my simple analysis of our 3D journey so far.

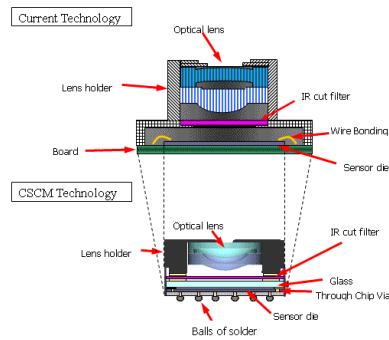

### The Birth of 3D

This may not be considered '3D integration' by many people (including me) but the CMOS image sensors (CIS) that use via-last through silicon via (TSV) interconnect technology were a very significant step in the commercialization of 3D. The Industry started to discover layers could be stack on top of each other with direct connections, and with much higher performances than die stack using wire bonds. This was the starting point.

### The teenage years

Stacking memory dies and application process engines in high-end cell phones (now known as smartphones) was identified as

a potential killer application to deliver high bandwidth at lower power consumption and with very small vertical dimension. However, thermal budget constraints and business model/supply chain limitations killed the high hopes. Hopefully, Xilinx and AMD made them in a slightly different way. However, the volume they manufactured cannot be compared to how things would have been if a flagship smartphone manufacturer had decided to embark on using wide IO memory with processor. In the meantime, cell phones started using TSMC's integrated fan-out (InFO) in a package-on-package (PoP) configuration, which was already a great achievement with significant benefits.

### Endless opportunities

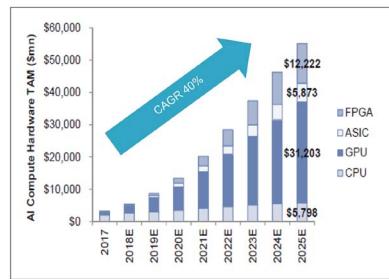

I still believe that system-on-chip (SoC) disintegration with IP blocks designed at their optimized technology nodes and then stacked on top of each other could happen. This is the next step after the new system-in-package (SiP) development we see now, and it should be part of the heterogeneous integration roadmap. The recent announcement of Intel's Foveros in December 2018 confirms this is likely happening.

Let's see what 2019 brings to us!

## 3D Powered: From Image Sensors to Edge Computing

**By Paul Werbaneth, Nor-Cal Products, Inc.**

The widespread deployment of 3D stacked CMOS Image Sensors (CIS) in consumer electronics, namely smartphones, by handset makers domestic (Apple, iPhone) and overseas (Samsung, Galaxy), is certain proof that 3D integration technologies pivoted over the last ten years from being something useful only for fairly esoteric applications and high ASP products, to being a technology that reached the right market, at the right cost, at the right time, in volumes high enough to push yields up, costs down, and, in Sony's case particularly, put money in the bank.

### An exploding market

According to Yole Developpement, as reported by Peter Clarke, "The (CIS) market was up 19.8% from \$11.6B in 2016 mainly driven by smartphones and the desire to add improved cameras. However, Yole believes the CMOS image sensor has a bright future driven by new applications in autonomous vehicles and industrial and machine vision. By 2023 Yole predicts the annual market will have climbed to more than \$23B, a compound annual growth rate of 9.4% from 2017 to 2023." That's a lot of Simoleans. And that's a lot of CIS.

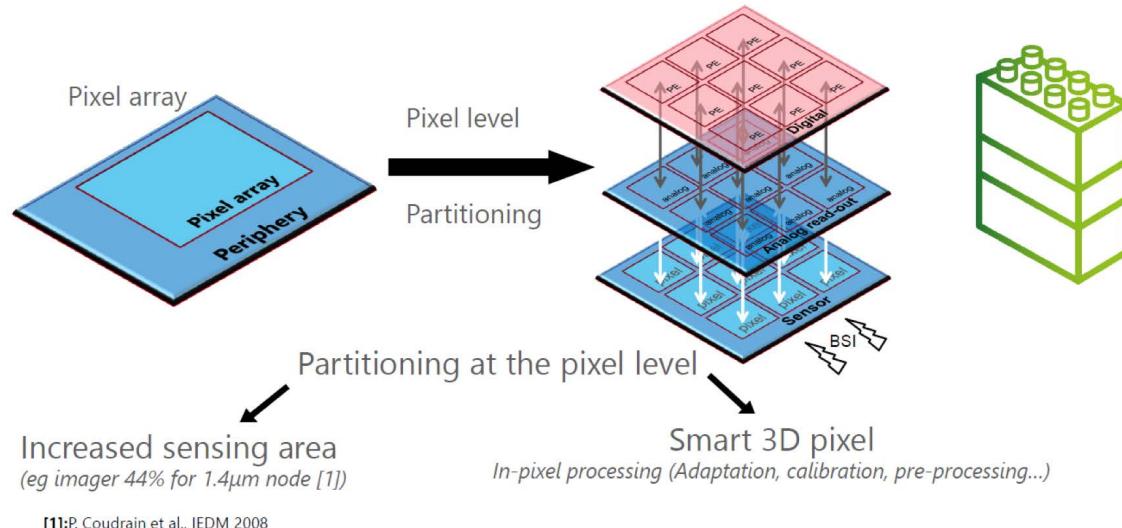

As Coventor reports, "A 3D-stacked image sensor consists of a back-side illuminated (BSI) image-sensor die, face-to-face stacked on a logic die. The motivation to invest in stacked chip BSI CIS development has been varied depending

upon the manufacturer but can be summarized as: 1) adding functionality; 2) decreasing form factor; 3) enabling flexible manufacturing options; and 4) facilitating optimization for each die in a 3D stack."

### Who talks on their phone anymore?