# 3DInCites<sup>TM</sup>

EST. 2009

## YEARBOOK

**COVER STORY:**

Looking ahead to

inspire the innovators

of the future

**Page 12** IFTLE 500: We've

come a long way, baby!

**Page 30** Through the

Eyes of our Interns

**Page 38** Community

reflections on 2021,

and what's to come...

ASE GROUP

## *The semiconductor chip*

Heroic and hip

From home to health

Applications in stealth

Enabling digital life

Alleviating global strife

Through intelligence

And limitless relevance.

## *ASE integration and packaging*

Tremendously advantaging

Performance and function

38+ years in production

Flip chip to fan out

R&D goes all-out

Connect to collaborate

And together we'll innovate.

[www.aseglobal.com](http://www.aseglobal.com)

# CONTENTS

4 Contributing Authors

7 Editorial - Keeping Up with the Times

**20 ON THE COVER**

Looking Ahead to Inspire the Innovators of the Future

A Conversation with KLA's Lena Nicolaides

By Françoise von Trapp, 3D InCites

9 Looking at the Global Semiconductor Expansion Through Polarized Lenses

By Dean Freeman, FTMA

12 IFTLE 500: We've Come a Long Way, Baby!

By Phil Garrou, 3D InCites

16 Adaptive Control: The "Holy Grail" in Semiconductor Manufacturing

By Dongkai Shangguan, Ph.D., Adaptix

26 Considerations in Power Amplifier Package Design

By Casey Krawiec, StratEdge

28 Vehicle Electrification Driving Supply Chain Evolution

Dr. Ajay Sattu, Amkor Technology, Inc

30 Through The Eyes of Our Interns

Featuring Matt Bowie, Brewer Science; Louise Greco, StratEdge; Devan Medeiros, Mosaic; Bhaumi Panchal, ERS Electronic GmbH; Maten Utschen, EV Group; Dolores Termini, Veeco

35 Sustainability Report Card: How Does Your Company Measure Up?

By Julia Goldstein, JLFG Communications

**38 SPECIAL SECTION**

3D InCites Community Reflections from 2021, and What's to Come in 2022

38 Where Is Semiconductor Packaging Design Headed?

By Keith Felton, Siemens EDA

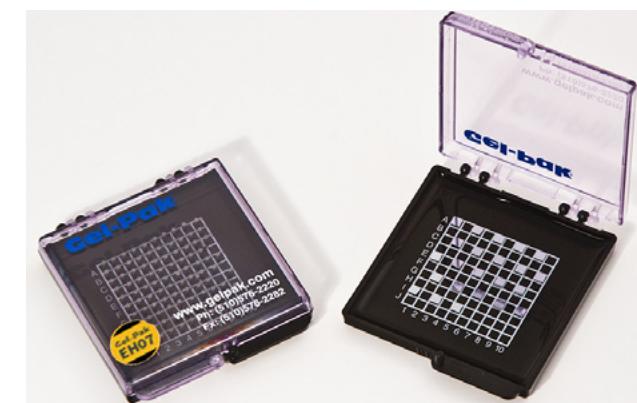

39 Protecting Devices During a Supply Chain Shortage

By Joe Montano, Delphon

40 Breaking Records in 2021 Despite COVID-19

By Peter Dijkstra, Trymax Semiconductor

41 Making the Impossible Possible: Building a Better Future

After a Year of Surprising Growth and Rising Demand

By Michael Plisinski, Onto Innovation

# CONTENTS CONTINUED

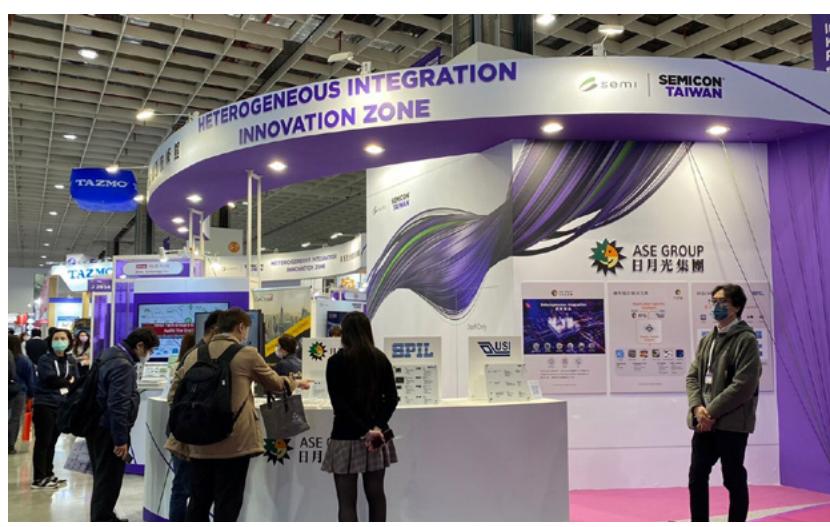

41 ..... **Another Strong Year Ahead for Hybrid Bonding Thanks to Heterogeneous Integration**

By Thomas Uhrmann, EV Group

42 ..... **Wafer-Level Packaging Is Well-Positioned for Growth**

By Sally-Ann Henry, ACM Research

43 ..... **Staying Ahead of the Advanced Packaging Technology Curve**

Rezwan Lateef, YES

44 ..... **The Foundation is Set: Ready for Growth in 2022**

By John Voltz, Reno Sub-Systems

45 ..... **From Chaos to Opportunity**

Patricia MacLeod, ASE

46 ..... **2021 In Pictures**

## STAFF

**Françoise von Trapp**

**Editor-in-Chief**

Francoise@3DInCites.com

Ph: 978.340.0773

**Martijn Pierik**

**Publisher**

Martijn@3DInCites.com

Ph: 602.366.5599

**Trine Pierik**

**Membership Director**

Trine@3DInCites.com

Ph: 602.366.5696

**Steffen Kröhnert**

**European Sales**

steffen.kroehnert@espat-consulting.com

Ph: +49 172 7201 472

**Danielle Friedman**

**Director of Operations**

Danielle@3DInCites.com

Ph: 602.443.0030

**Phil Garrou**

**Contributing Editor**

PhilGarrou@att.net

**Dean Freeman**

**Contributing Editor**

freconsult@gmail.com

### Creative/Production/Online

**Scott Timms**

Lead Designer

**Ale Moreno**

Web Developer

### Technical Advisory Board

**Sitaram R. Arkalgud, Ph.D.**

Tokyo Electron, USA

**Rozalia Beica**

AT&S, Austria

**Pascal Couderc**

3D PLUS, France

**Yann Guillou**

Applied Materials, USA

**Dr. Phil Garrou**

Microelectronic Consultants

of NC, USA

**Erik Jan Marinissen**

IMEC, Belgium

**Peter Ramm**

Fraunhofer EMFT, Germany

**Herb Reiter**

eda2asic Consulting, USA

**Mark Scannell**

CEA-Leti, France

**Dr. Maaike M. Visser Taklo**

Sonitor Technologies, Norway

**E. Jan Vardaman**

TechSearch International, Inc.

**Paul Werbaneth**

Ichor Systems, Inc.

**M. Juergen Wolf**

Fraunhofer IZM-ASSID, Germany

### Visit us at [www.3DInCites.com](http://www.3DInCites.com)

Subscribe to our e-newsletter, *3D InCites In Review*: <https://www.3dincites.com/subscribe-newsletter/>

The *3D InCites Yearbook* is published by:

3D InCites, LLC

45 West Jackson St. Suite 700

Phoenix, AZ, 85003

Ph: 602.443.0030

Copyright ©2022 by 3D InCites, LLC.

All rights reserved. Printed in the US.

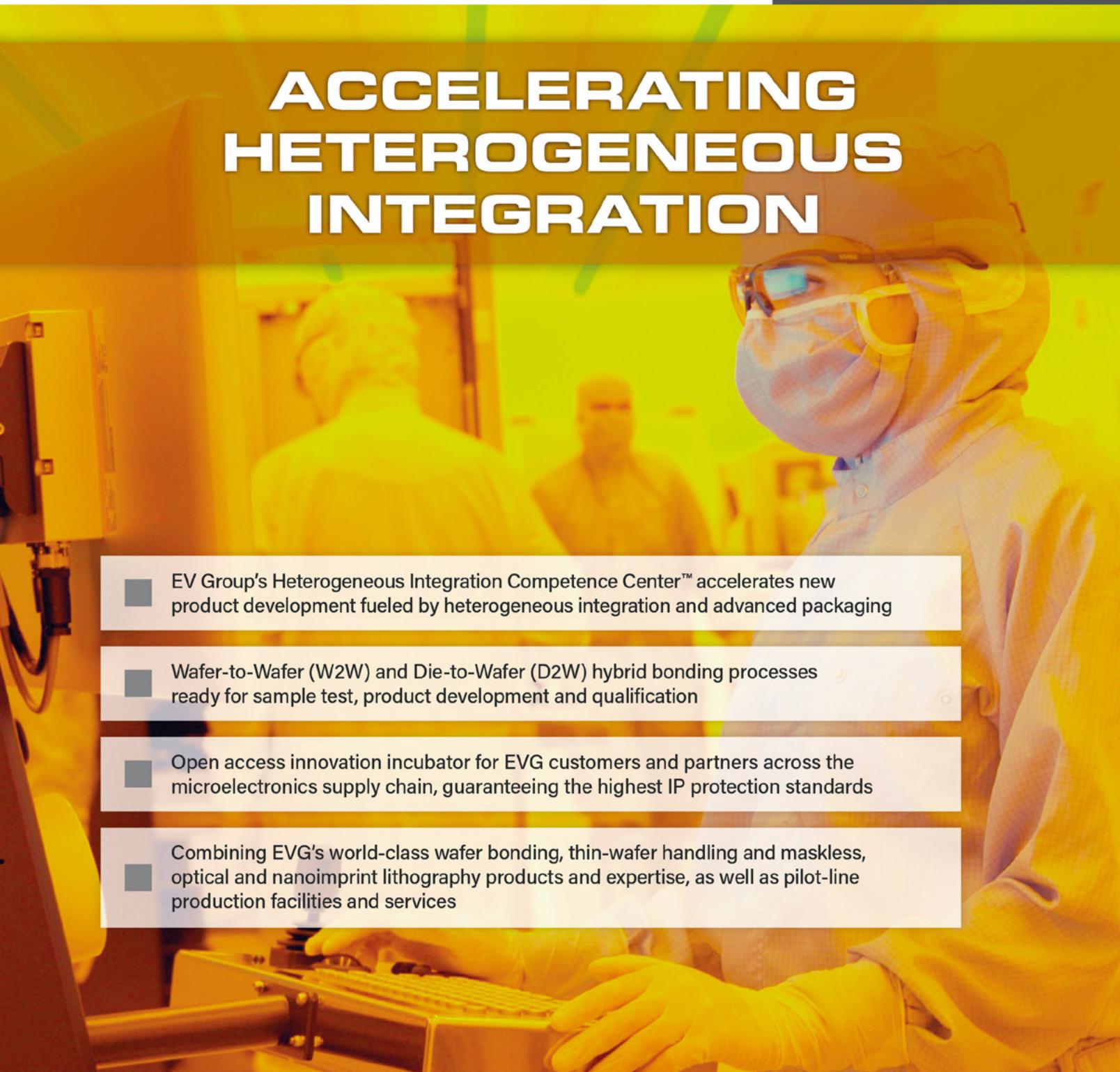

## ACCELERATING HETEROGENEOUS INTEGRATION

■ EV Group's Heterogeneous Integration Competence Center™ accelerates new product development fueled by heterogeneous integration and advanced packaging

■ Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding processes ready for sample test, product development and qualification

■ Open access innovation incubator for EVG customers and partners across the microelectronics supply chain, guaranteeing the highest IP protection standards

■ Combining EVG's world-class wafer bonding, thin-wafer handling and maskless, optical and nanoimprint lithography products and expertise, as well as pilot-line production facilities and services

GET IN TOUCH to discuss your manufacturing needs

[www.EVGroup.com](http://www.EVGroup.com)

# CONTRIBUTING AUTHORS

**Peter Dijkstra**, the author of *Breaking Records in 2021 Despite COVID-19*, is Chief Commercial Officer at Trymax

Semiconductor. He joined the team in 2021, coming from ASM Pacific Technology, where he served as director of sales, service, and marketing from 2014-2021. Before ASM, Peter spent his career working with plasma-based technologies in the semiconductor equipment space, including ALSI, Nanoplas, Tegal, and Alcatel, and the Plasma Physics Research lab.

**Keith Felton**, the author of *Adapting to Virtual Communications*, is the Marketing Manager for Xpedition IC

Packaging solutions at Siemens, driving the strategy and direction for multi-substrate prototyping, design, and verification solution for high-density advanced packages. He has worked extensively in the area of IC package design since the late 1980s. In the early 2000s, Keith drove the launch of the industry's first dedicated system-in-package design solution. In 2017 he led a team that launched Mentor's OSAT Alliance program. Before Siemens, Keith was Group Director of Product Marketing at Cadence Design Systems.

**Dean W. Freeman**, the author of *Global Fab Expansion*, is Chief Analyst at FTMA. With more than 36 years

of semiconductor manufacturing and materials experience, Dean is known for his role as market research VP for Gartner tracking the semiconductor manufacturing, process technology, and the Internet of Things. He has also worked at FSI, Watkins Johnson, Lam Research, and Texas Instruments. He holds nine process and equipment patents and has published multiple articles in various trade and technical journals.

**Philip Garrou, Ph.D.**, the author of *IFTLE, We've Come a Long Way, Baby!*, is a subject matter expert for DARPA

and runs his own consulting company, Microelectronic Consultants of NC. He is well known for his weekly advanced packaging blog, *Insights from the Leading Edge*. Since retiring from Dow Chemical, Phil has served as Technical VP and President of both IEEE EPS and IMAPS and is a Fellow of both organizations.

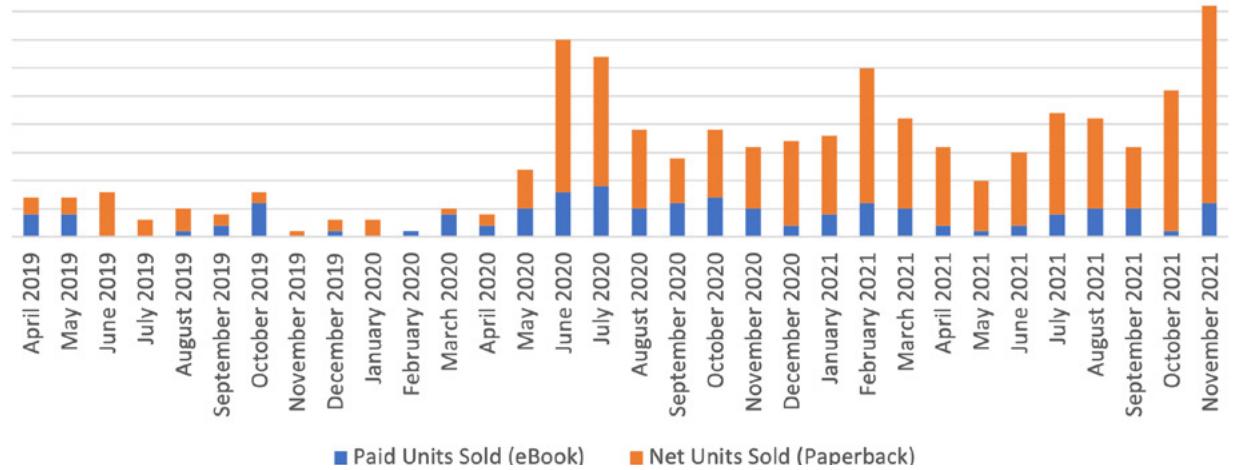

**Julia Goldstein**, the author of *Sustainability Report Card, Does Your Company Measure Up?*

is principal at JLFG Communications, LLC. She is a writer and author with a materials science background, trade press experience, and the desire to never stop learning. She shares her passion for materials and sustainability in her book *Material Value*, published in 2019. *Material Value* was a B.R.A.G Medallion Honoree, Finalist in the 2019 San Francisco Writers Contest, and Semifinalist for the 2020 Nonfiction BookLife Prize.

**Rezwan Lateef**, the author of *Staying Ahead of the Advanced Packaging Technology*

Curve, has been president of YES since November of 2020, after two years as the company's SVP of Sales & Service. He has over 15 years of experience in the semiconductor industry and was a key executive in the successful sale of two companies. He has also held leadership positions at MKS, NEXX Systems, TEL, Ultratech & Veeco.

**Casey Krawiec**, the author of *Considerations in Power Amplifier Package Design*, is Vice President of Global Sales for

StratEdge Corporation. He has worked for companies involved with wafer preparation, microelectronic assembly, and packaging for over 25 years. After earning a BS in Mechanical Engineering from the University of Kentucky and an MBA from the University of Louisville, Casey was a design engineer for the Department of Defense for several years. He worked at StratEdge from 2002 to 2009 and then returned to StratEdge in 2018.

**Sally-Ann Henry**, the author of *Wafer-Level Packaging Is Well-Positioned for Growth*, is a seasoned

semiconductor leader, visionary, and process professional who has deep expertise in semiconductor back-end-of-line product management, planning, quality systems, and worldwide customer relationship management. In her role as a business development leader at ACM Research, she excels at working cross-culturally to solve semiconductor process issues across Europe, Asia, and the United States.

**Michael Plisinski**, the author of *Making the Impossible Possible: Building a Better Future After a Year of*

*Surprising Growth and Rising Demand*, is chief executive officer at Onto Innovation. He has 25 years of semiconductor capital equipment experience, beginning with founding Counterpoint Solutions in 1999, through its subsequent acquisition by August Technology Corporation in 2003. He continued to hold significant leadership roles at August, and then Rudolph Technologies, after the merger of those two companies. In 2015, he became CEO and a member of the board of directors at Rudolph, leading the company through the merger with Nanometrics to form Onto Innovation.

**Joe Montano**, the author of *Protecting Devices During a Supply Chain Shortage*, joined the Delphon team in late

2020 as President and was recently appointed to the position of President and CEO effective January 1, 2022. He has spent his entire 25+ year career in electronics and electronic materials technology segments, with experience spanning from the R&D bench to Sr. VP positions and now President and CEO. Before joining Delphon, Joe was the Global Business Director for MacDermid Enthone's Advanced Electronics division before moving to Sr. VP of Sales and Marketing for Intermolecular Inc. There, he helped orchestrate the acquisition of Intermolecular by Merck KGaA, Darmstadt, Germany in 2019.

**Ajay Sattu**, the author of *Vehicle Electrification Driving Supply Chain Evolution* joined Amkor in 2018 and is

Director, Automotive Product Marketing at Amkor Technology, Inc. He is focused on automotive electrification, ADAS, and infotainment product marketing and strategy. Before joining Amkor, he worked for Infineon, managing the technology and

product development of wide-bandgap semiconductors. Ajay has published more than ten articles and presented at several conferences in the emerging technologies area of GaN and SiC.

**Dongkai Shangguan, Ph.D.**, the author of *Adaptive Control: The "Holy Grail" in Semiconductor*

*Smart Manufacturing*, is an IEEE Fellow and IMAPS Fellow, currently advises several innovative companies in the global electronics industry. Previously, he served as Corporate Vice President for Advanced Manufacturing Engineering at Flex (formerly Flextronics), and as Chief Marketing Officer at STATSChipPAC (currently JCET). A recipient of numerous awards, Dongkai has published two books, authored/co-authored over 300 technical papers and articles, and has been issued over 20 patents.

**John Volz**, the author of *The Foundation is Set: Ready for Growth in 2022*, is Senior Vice President Business Development

- Office of the President, Reno Sub-Systems. An industry veteran with 35 years of semiconductor capital equipment experience, John comes to Reno from Ferrotec's Temescal division, where he was Business Development Director. Before that, John held leadership roles at SSEC LLC, Genus, Inc., Matrix Integrated Systems, Inc., Mattson Technology, Inc.; and various management positions at Silicon Valley Group, Inc. and Plasma and Materials Technologies, Inc.

**Dr. Thomas Uhrmann**, the author of *Another Strong Year Ahead for Hybrid Bonding Thanks to Heterogeneous*

Integration, is director of business development at EV Group where he is responsible for overseeing all aspects of the company's worldwide business development. Before this role, Uhrmann was the business development manager for 3D and advanced packaging as well as compound semiconductors and Si-based power devices at EV Group. He holds an engineering degree in mechatronics from the University of Applied Sciences in Regensburg and a Ph.D. in semiconductor physics from the Vienna University of Technology (TU Wien).

## Intern Experience Bios

**Matthew Bowie**, the author of *What's It Like to Intern at A Top Workplace Award Winner*, is a printed

electronics intern at Brewer Science as part of his pursuit of a degree in Electrical Engineering at Missouri University of Science and Technology.

**Devan Medeiros**, the author of *How My Internship at Mosaic Helped Me Grow*, is a chemical

engineering student at Rochester Institute of Technology. He recently completed an 8-month internship at Mosaic Microsystems.

**Louise Greco**, the author of *From Macro to Micro: Learning Microelectronics Firsthand at StratEdge*, is an Engineering Tech at StratEdge & Aerospace Engineering student at Southwestern College.

**Bhaumi Panchal**, the author of *Why An Internship in Fan-out Technology Was My Dream Come True*, graduated from the University of Passau with a Master's degree in Mobile and Embedded Systems. She is currently working for ERS electronic as a Fan-out Product Engineer.

**Matan Utschen** is a Mechanical Engineering student at Arizona State University. He spent his internship at EV Group's North American HQ in Tempe Arizona.

**Dolores Termini** is currently a graduate student at the New Jersey Institute of Technology studying material science. Dolores earned her undergraduate Engineering degree with a focus on optics and lasers. She is currently an Applications Lab Intern at Veeco based in Somerset, New Jersey.

# Enabling the Future

As one of the world's largest providers of high-quality semiconductor packaging and test services, Amkor has helped define and advance the technology landscape.

We deliver innovative solutions and believe in partnering with our customers to bring 5G, AI, Automotive, Communications, Computing, Consumer, IoT, Industrial and Networking products to market.

As a truly global supplier, Amkor offers manufacturing and test capabilities as well as product development and support services in Asia, Europe and the US.

# Keeping Up with the Times

By Françoise von Trapp

That's one reason we started the **3D InCites Podcast** – to meet our audience through a medium that they use often. Who listens to podcasts? According to Edison Research's Infinite Dial Report, 49% of monthly U.S. podcast listeners are aged between 18-34, 40% between 35 and 54 years old, and 22% are aged over 55. Just look at how those numbers line up with ours!

I'm sitting here, flipping through memories of 2021 like it was a Rolodex, sorting through the highlights, lowlights, and Aha! moments to share with you in this Yearbook editorial. And then I realize I'm dating myself, because how many people under the age of 35 know what a Rolodex is? But an analogy to Hubspot or some other CRM — that's customer relationship management, for you old-timers — doesn't give the same mental picture so I'm sticking with it.

Why do I care if someone under the age of 35 understands my reference? Because believe it or not, one of my Aha! moments of 2021 was discovering, by the power of Google Analytics, that the largest segment of our readers (42%) falls between the ages of 18 and 34. And almost 38% falls between the ages of 35-54. In fact, only 20% of our readership is older than 55.

This is a pretty big deal. Because as more of the semiconductor industry workforce approaches retirement age, the talent shortage is worsening. It's more important than ever to reach a young audience — one that might consider a future in microelectronics and semiconductor manufacturing if they knew how interesting and exciting it is.

We've also dedicated this Yearbook issue to inspiring young engineers to pursue careers in the semiconductor industry. In our Cover Story, *Looking Ahead to Inspire the Innovators of the Future* (Page 20), I speak with Lena Nicolaides, Sr. VP, and GM at KLA, about the company's efforts in recruiting, retaining, and sustaining talent. KLA's initiatives extend from within the company itself, to the surrounding communities, reaching children as early as kindergarten age. Additionally, we invited interns at our member companies to submit essays on their internship experience, in the hope of inspiring others to join this exciting industry. Their stories begin on page 30.

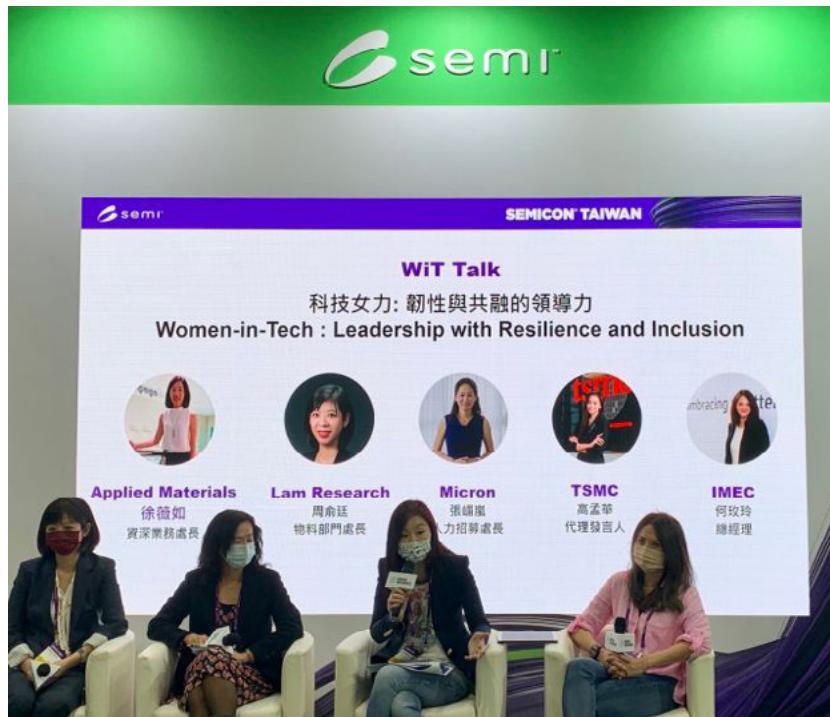

Getting back to in-person events was a major highlight of 2021. Steffen Kröhner represented 3D InCites at SEMI Europe's Packaging Technology Seminar and SEMICON Europa. I attended both the IMAPS International Symposium and SEMICON West and brought our podcast recording equipment along to capture all the conversations we've been missing over the past two years. You'll find photos beginning on page 46.

Both SEMI and IMAPS recognize the importance of reaching a younger audience. We're working with these industry organizations to help spread the word about the importance of sustainable semiconductor manufacturing and diversity equity and inclusion (DEI). We partnered with SEMI to be the Official Podcast of SEMICON West 2021, and plan to expand that relationship in 2022.

One of our first big moments of 2022 is becoming Official Industry Partners with the International Microelectronics Society (IMAPS). We've always had media trades, but as we recognize the synergies between our two organizations, we decided to formalize the relationship.

Our first order of business is to integrate the 3D InCites Awards and DEI fundraising more definitively into the IMAPS Device Packaging Conference agenda. Beth Keser, president of IMAPS, served as one of the technology judges and will help present the awards. Our Mural Fundraiser is happening again, and we're also hosting the first-ever Hike for DEI, sponsored by KLA. 100% of the proceeds from the mural and hike benefit the 3D InCites DEI Fund, established in 2021 to help tech start-ups owned by women and underrepresented minorities grow and thrive.

It goes without saying that the lowlight of 2021 was the emergence of the Omicron variant. Just when it looked like things were getting back to normal, there it was to remind us that COVID is something that we're going to be dealing with for some time to come. But don't let it get you down. Despite it, our industry is on an upward trajectory and we've all had a pretty good year. Remember that, and try to stay safe, everybody!

SurfaceSens™

## FLEXIBLE MULTI-SENSOR SURFACE MEASURING TECHNOLOGY

### Modular optical metrology set-up for hybrid surface process control

FormFactors FRT Metrology designed **SurfaceSens™** technology to achieve superior information about the measured sample and greater insights about the products quality. All our FRT MicroProf® metrology tools can be configured with complementary sensor technologies.

In a hybrid analysis process, otherwise inaccessible surface data of wafers or other samples are precisely measured. SurfaceSens offers you the possibility to combine unique metrology and inspection measuring principles in one single tool and thus allows maximum flexibility.

## Looking at the Global Semiconductor Expansion Through Polarized Lenses

By Dean Freeman, FTMA

The song, *Happiness is Lubbock Texas in My Review Mirror*, has a special meaning for me, as due to a Texas ice storm, a day trip to Lubbock, TX was extended. Thanks to a determined Southwest Airlines team, a group of us managed to get home only a day later, as opposed to potentially spending the weekend in Lubbock in the snow and ice.

As the semiconductor industry moves into 2022, I can't help but wonder if any executives are thinking: "Happiness is 2021 in the review mirror". Perhaps they have mixed feelings about a year riddled with ice storms in the southwest of the United States that shut semiconductor plants down, as well as droughts in Taiwan, a factory fire in Japan, shipping and supply chain issues for material, equipment, and semiconductor manufacturers, a hybrid work environment increasing manufacturing challenges, and a talent shortage. This has all contributed to the widely highlighted chip shortage. That, paired with unprecedented demand due to what could be called a paradigm shift in the electronics industry due to electric vehicles (EV), 5G, smart everything, and edge computing, is making things interesting, to say the least.

However, even with all the challenges, this has been a banner year for the microelectronics industry. From a chip perspective, the Semiconductor Industry Association (SIA)s fall forecast has the industry ending 2021 at 25.6% growth. This equates to \$553 billion in growth for 2021, the strongest growth year since 2010. From an equipment and materials perspective 2021, according to a recent press release by SEMI, total equipment is expected to reach a historical high of \$103 billion, 44% year over year growth, with WFE reaching 88 billion, and the assembly and packaging sector just shy of \$7 billion, and test at \$8 billion.

**IC Insights estimates** that total Capex will reach \$152 billion; also a historical high. The market research firm says these strong growth rates have been driven mostly by logic and analog expansion. The top four equipment companies— Applied Materials (AMAT), ASML, Lam Research, and TEL — all look like they will top the \$10 billion mark for equipment sales, and ASML looks like it has close to a 12-month backlog going into 2022 (Figure 1).

As the industry moves into 2022, most CEOs seem to be cautiously optimistic on their quarterly calls, but as this industry has learned over time, the outlook can change

Figure 1: SEMI 2021 Year-end total equipment forecast by segment. (Source: SEMI)

in the blink of an eye. The last time I remember ASML having a 12-month backlog, the outlook changed very quickly as I'll discuss below.

#### What Will 2022 Bring?

What does this mean for 2022? At first look; good news. In its **December press release**, the SIA is forecasting an 8.8% growth in semiconductors. **IC Insights** is predicting 11% growth. So, from a chip perspective, the growth will continue. This is being driven, in part, by the extended chip shortage.

Many articles written on the shortage have the tightness or shortages extending through at least the first half of 2022 and possibly longer. However, this pertains mostly to logic and particularly automotive, due to the increasing demand for electronics in automobiles. The SIA forecast shows fairly even revenue growth across all sectors for 2022, perhaps suggesting that supply and demand will come further into balance in 2022, and the shortage will start to dissipate (Figure 2).

#### On the Equipment Side

From an equipment perspective, SEMI is predicting 11% growth in 2022 after a staggering 44% growth in 2021. The 11% for equipment growth for 2022 seems to be close to the consensus from the earnings calls from the "Big Four" equipment companies. In 2023, SEMI is predicting a very slight downturn.

This is where it gets a bit interesting. Ajit Manocha, President, and CEO of SEMI presented the following at SEMICON West: Between 2020 and 2024 a significant number of fabs will be built. Twenty-five 200mm fabs and 60 300mm fabs. This accounts for 18% capacity growth for 200mm and 48% growth for 300mm in the 2020–2024-time frame. For 200 mm 14 of those 25 fabs are in China, two in Taiwan, and

three in Japan. For the 300mm fabs, 15 are in China and 15 are in Taiwan. Six are targeted for the United States, and Europe and Israel are seeing a significant increase in activity as 10 are targeted for Europe and the Middle East. This suggests the potential for strong growth for the foreseeable future. Especially since it appears that China will continue to build no matter what the environment.

Another positive out of this fab forecast is that there is little to no inventory for 8-inch used equipment. This means that unless that 200mm fabs have a source for 200mm equipment, they will be buying new equipment, which will then have a significant impact on margins due to paying off that newer equipment. I suspect this might slow the start-up of some 200mm fabs, but also be extremely beneficial to 200mm equipment suppliers.

#### So, What Could Go Wrong?

Chip demand is currently extremely strong. Consumers in the United States are fueling electronics demand. The automotive industry needs to catch up and build inventory. 5G is rolling out, as is WiFi6, and industry is digitizing which strengthens demand for cloud computing, and artificial intelligence (AI).

#### What can slow the industry down?

There are the usual suspects. Covid 19, a talent shortage, trade issues.

| Fall 2021                      | Amounts in US\$M |                |                | Year on Year Growth in % |      |      |

|--------------------------------|------------------|----------------|----------------|--------------------------|------|------|

|                                | 2020             | 2021           | 2022           | 2020                     | 2021 | 2022 |

| <b>Americas</b>                | <b>95,366</b>    | <b>118,835</b> | <b>131,084</b> | 21.3                     | 24.6 | 10.3 |

| <b>Europe</b>                  | <b>37,520</b>    | <b>47,126</b>  | <b>50,467</b>  | -5.8                     | 25.6 | 7.1  |

| <b>Japan</b>                   | <b>36,471</b>    | <b>43,581</b>  | <b>47,621</b>  | 1.3                      | 19.5 | 9.3  |

| <b>Asia Pacific</b>            | <b>271,032</b>   | <b>343,419</b> | <b>372,317</b> | 5.1                      | 26.7 | 8.4  |

| <b>Total World - \$M</b>       | <b>440,389</b>   | <b>552,961</b> | <b>601,490</b> | 6.8                      | 25.6 | 8.8  |

| <b>Discrete Semiconductors</b> | <b>23,804</b>    | <b>30,100</b>  | <b>32,280</b>  | -0.3                     | 26.4 | 7.2  |

| <b>Optoelectronics</b>         | <b>40,397</b>    | <b>43,229</b>  | <b>45,990</b>  | -2.8                     | 7.0  | 6.4  |

| <b>Sensors</b>                 | <b>14,962</b>    | <b>18,791</b>  | <b>20,913</b>  | 10.7                     | 25.6 | 11.3 |

| <b>Integrated Circuits</b>     | <b>361,226</b>   | <b>460,841</b> | <b>502,307</b> | 8.4                      | 27.6 | 9.0  |

| Analog                         | 55,658           | 72,842         | 79,249         | 3.2                      | 30.9 | 8.8  |

| Micro                          | 69,678           | 79,102         | 83,980         | 4.9                      | 13.5 | 6.2  |

| Logic                          | 118,408          | 150,736        | 167,396        | 11.1                     | 27.3 | 11.1 |

| Memory                         | 117,482          | 158,161        | 171,682        | 10.4                     | 34.6 | 8.5  |

| <b>Total Products - \$M</b>    | <b>440,389</b>   | <b>552,961</b> | <b>601,490</b> | 6.8                      | 25.6 | 8.8  |

Figure 2: World Semiconductor Trade Statistics (WSTS) Forecast Summary (Source: WSTS) Note: Numbers in the table are rounded to whole millions of dollars, which may cause totals by region and totals by product group to differ slightly.

To me, these are minor bumps in the road and, except for the trade issue, can be resolved with some creative thinking, such as training programs, which used to exist when I entered the industry. My concerns are something bigger on the horizon.

The first is what instigated the last major downturn in the industry. In 2008 and 2009 wafer fab equipment (WFE) declined 32% and 46% respectively due to the Lehman Brothers financial crisis. Going into SEMICON West 2008, equipment backlogs were 6-12 months, the future looked very bright. and then three months later the industry was scrambling. According to the **Chip History website**, analysts were not aware of the impending crisis. Some analysts were concerned, but the hot electronics market and the huge WFE backlogs made it difficult to send a message of doom and gloom.

So, what does the Lehman crisis have to do with today's market? While in the western world the financial markets are in pretty good shape. In China, multiple bankruptcies are in progress. Evergrande real estate, and **The Tsinghua Unigroup**, parent of YMCT, are both struggling financially and are working to restructure.

While the total debt of both companies is well under 500 billion, there are some thoughts that this could cause a significant financial crisis in China. If **Evergrande** fails and does not get bailed out, it

is likely there will be a slowing of investment in new projects. If YMCT goes under, there would probably be a limited impact on the NAND business, but there could be a shock wave for the equipment industry, as there could be a pullback on those 29 new fabs scheduled to start-up in the next two years. It is a challenging situation to predict. Beijing may help to avoid any crisis, but it is also possible Beijing will let the companies fail. It happened in the LED industry when it was overbuilt in China a while back, so it could also happen in this situation. Currently, it is a wait-and-see situation.

The US/China trade issues also cloud the future of the equipment outlook. From my perspective, the US Government trying to stop China's chip and electronics expansion are a bit like trying to put the toothpaste back in the tube, since previous administrations encouraged electronics growth in China.

There is always the outside chance the commerce department will prohibit the sales of US semiconductor equipment to any fab in China, and pressure U.S. allies to follow suit. In the near term this would make the semiconductor shortage even worse, and in the long term have the potential of US or European companies reshoring parts

**"Happiness is 2021 in the review mirror. HAPPINESS IS A FULLY LOADED FAB"**

of that chip business. However, this transition would take at a minimum, 4-6 years, and it would need significant government financing, significantly more than the current, hopefully-by-the-time-you-read-this passed, CHIPS act is proposing.

In the short term, it would reduce the semiconductor equipment sales by approximately 25% until that chip business was relocated.

It would also potentially create the opportunity for the Chinese equipment makers to up their game and develop competitive products for the Chinese market.

The other upcoming challenge for the industry is the inevitable oversupply of chips that will be created by all of these new fabs. Economics has driven the chip industry. Economics has driven the fabless model and made TSMC the success it is today. I don't remember the source, and I probably have written it in these blogs before, but "Happiness is a fully loaded Fab". The oversupply probably won't happen in 2022, but maybe that's why SEMI has a flat forecast predicted for 2023.

So, while at the moment, the future of the semiconductor chip, packaging, and equipment industry looks very bright, I'm making sure I'm wearing my polarized lenses so I can hopefully see the contrasts as they come down the road.

#### HEXAGON – the tool that gives you more in wafer level packaging

With **more** productivity than ever, Evatec's new HEXAGON is the perfect choice for thin film wafer level packaging processes including FOWLP and WLCSP. Add in **more** process flexibility, **more** uptime and a **more** compact design taking up less valuable fab space and it's easy to see how the new HEXAGON simply gives you **more**. To find out about the new HEXAGON watch the short video or contact your local sales and service organisation. Welcome to HEXAGON – the future in thin film production for wafer level packaging applications.

# IFTLE 500: We've Come a Long Way, Baby!

By Phil Garrou, 3D InCites

Insights from the Leading Edge (IFTLE) believe it or not, has reached #500! I hope this message reaches all of you free of COVID and ready to move on in this exciting period for Advanced Microelectronic Packaging. For those of you that have not been on board for the full trip, let me share a little background history.

## Background 2004-2010

After retiring early in 2004 following a 27-year career at Dow Chemical, I started writing Advanced Packaging articles for Pete Singer and his leading microelectronics magazine, "Semiconductor International" (SI). While SI's focus was on front-end chip fabrication, there was readership interest in the leading packaging technologies of the day.

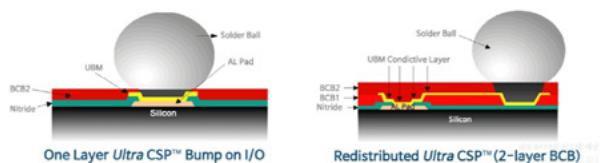

Post-2000 wafer-level packaging (WLP) was just beginning to catch on as Pete Elenius and Flip Chip Technology (FCT) began licensing its bumping and WLP technology to all the major packaging houses in Taiwan and Korea. WLP was of special interest to me since, while at Dow, my electronics business had helped FCT develop its "Ultra CSP" WLP and low-cost bumping technologies with our Benzocyclobutene resin (BCB) (Figure 1).

Figure 1: Versions of FCT's Ultra CSP WLP.

In 2005, Kenny Williams at the Microelectronics Center of NC, hired me part-time to help with its new DARPA 3DIC program and I quickly became convinced that vertical integration was the next big thing. I knew from the beginning that this technology would take substantial time to catch on, but little did I know how long it would take. My 2005 article, "Future IC's Go Vertical", was one of the earliest magazine articles of the 3D IC genre and one of the most highly referenced at the time.

My early SI articles included:

- October 2000 - "Wafer Level Packaging Has Arrived"

- Oct 2004 - "The Wafer Level Packaging Evolution"

- Feb 200 - "Future ICs Go Vertical"

- October 2006 - "Wafer-Level 3D Integration Moving Forward"

- Dec 2006 - "Opto- WLPs for CMOS Image Sensors"

- April 2007 - "Posturing and Positioning in 3D ICs"

- Oct 2008 - "3D ICs Coming Together"

- Nov 2008 - "3D ICs Enter Commercialization" (Figure 2)

Figure 2: Phil was a regular contributor to SI and penned many articles on hot packaging topics.

In 2006, I rose to the rank of "Editorial Advisor". By the summer of 2007, it had become obvious that SI was shrinking in page count due to fewer and fewer print advertisers, and that internet publications had become the wave of the future. At that point, Pete asked me to think about a weekly blog to keep the world updated on what was going on in Advanced Packaging.

On July 28, 2007 "Perspectives From the Leading Edge" (PFTLE) was born with the first blog being a little personal bio and a promise ..... "For all the latest in advanced packaging stay linked to PFTLE....."

Figure 3: Back row: Xie (Penn State), van Doremalen (Philips), Garrou, (Microelectronic Consultants of NC), Tanaka (U. Tokyo), Patti (Tezzaroni), Shaper (U. Arkansas), Enquist (Ziptronix), Morrow (Intel), Keast (MIT LL), Front row: Motoyoshi (Zycube) Aoyagi (AIST), Beyne (imec), Koyanagi (Tohoku U) Yamada (IBM Japan), Kada (ASET), Lu (RPI), Franzon (NC STATE), Patel (Altera).

Over the next few years, I developed my irreverent reporting "style", which included a blend of hard-hitting technical content mixed with sarcasm and tongue-in-cheek humor in articles such as :

- *Going Vertical in Whitefish* - 09/09/2007

- *What's the Capital of NY State?* - 10/14/2007

- *A Rose by any Other Name is NOT 3DIC Integration* - 11/20/2007

- *3D Integration: Evolution or Revolution?* - 03/16/2008

- *If It's Thursday this must be San Jose* - 06/08/2008

- *It All Depends on What the Meaning of 'it' Is* - 09/17/2008

- *Mechanical Bulls, Rollercoasters, and CIS with TSV* - 09/26/2008

- *Ziptronix Opens the Kimono* - 10/14/2008

- *Like Mick Jagger said: You Can't Always Get What You Want* - 11/24/2008

- *Fisk, Buckner, and Pasta in the North End* - 12/31/2008

- *Like Swallows Returning to San Juan Capistrano* - 03/20/2009

- *Ginkgo Biloba* - 09/12/2009

Having been editor of my high school newspaper years before (Brooklyn Technical HS class of '66), I knew all about clever headlines and having roots in the bowels of Hell's Kitchen, NYC, it was impossible for me not to be sarcastic and/or tongue in cheek when I wrote.

Figure 4: Phil's Four Horsemen of 3D IC integration – cost, test, thermal management, and design.

By the time we published PFTLE 100 in 2009, we were covering the presentations at the first global conference focused on 3DIC sponsored by the IEEE CPMT Society (now the IEEE EPS (Electronics Packaging Society) and chaired by Paul Franzon and me. Figure 3 captures the organizing committee, a veritable who's who for 3DIC in 2009.

A few months later PFTLE, introduced the Four Horsemen of 3DIC Integration": Cost... Test...

Thermal Management...Design, to emphasize that more was needed than the basic process flow before commercial 3D stacking could be introduced into the mainstream market (Figure 4).

In early 2010, with much of the 3D unit operation processing work behind us, PFTLE began to focus on efforts of standardization, which most agreed had to start with memory stacks.

Then, after 128 weekly blogs, in April of 2010, Reed Elsevier, the owners of SI sold off its magazine portfolio and pulled the plug on Semi International. As the SI web pages were shut down so were the links to all my work! Lesson for all current and future bloggers ...Internet blogs are not archival!

## IFTLE Begins – 2010

Pete Singer quickly moved over to PennWell publishers and the newly merged (2009) Advanced Packaging / Solid State Technology franchise and brought me with him. There were worries concerning the copyright on "PFTLE", so I reluctantly changed the title to "Insights from the Leading Edge (IFTLE)" and thus it has remained ever since. In June of 2010 we were back online as IFTLE with the following statement:

As Jack Nicholson said in the Stephen King classic "The Shining" ...I'm baaack...!

That first IFTLE covered updates from the 2010 Electronic Component Technology Conference (ECTC), and an announcement that the IEEE had bought out the EIA and now had full ownership of the ECTC conference. I was especially proud of that last item since I had been working on accomplishing that acquisition for several years during my IEEE Electronic Packaging Society (EPS) [at that time known as CPMT] presidency and that of Bill Chen who followed me.

The relationship with PennWell's Advanced Packaging/ SST franchises worked well for nearly 8 years and 395 IFTLE blogs, but I could see trouble was brewing once again towards the end of this period when contributors' checks were being delayed for many months at a time. There was always some excuse, but the inevitable closure finally came.

Phil Garrou and Françoise von Trapp celebrate during the 2018 3D InCites Awards.

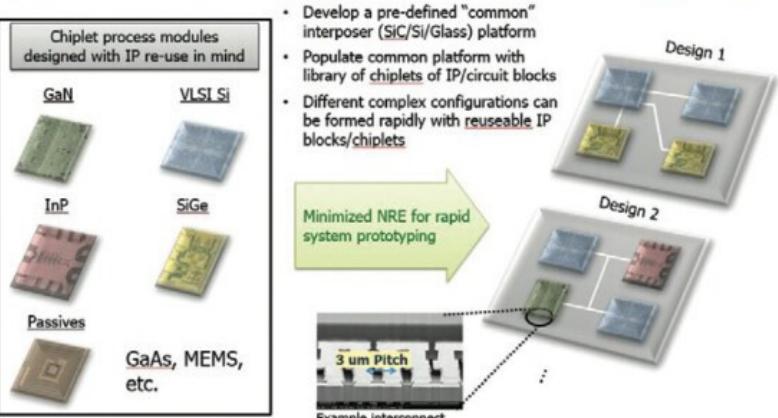

program, which had started in 2017, and of which I was a participant. This of course was the precursor to today's chiplet mania in the advanced packaging community (Figure 5).

Things at 3D InCites for the **100+ blogs** have gone as smooth as silk. Thanks to **FRT (now Formfactor)** who sponsored IFTLE for 2 years, and to our current sponsor, **EV Group**.

Looking back, there have been several things that I have intentionally tried to do with IFTLE.

The number one premise for this blog has always been to share with our worldwide readership what was being presented at the major and minor conferences held around the world on topics pertaining to Advanced Packaging. There are very few of us who have the budget or time to allow us to personally attend all these meetings, so PFTLE/IFTLE thought we could try to share what went on and get that information back to our readership.

#### DARPA Integration: Enabling IP and Chiplet Re-use

Figure 5: Phil kicked off his tenure at 3D InCites with a post about the DARPA CHIPS Program.

This time I acted quickly and talked to my old friend, Françoise von Trapp who had established the 3DInCites community back in 2009. Seemed like a good spot to re-establish IFTLE and she was quick to welcome me on board. This time I kept the IFTLE acronym and we started up with number 396 with an update on the **DARPA CHIPS**

But, instead of covering these meetings the way traditional reporters would with inconsequential comments from authors or titles and a one-line summary, IFTLE selected key presentations and shared the key slides from those presentations. Did I always pick out the most important papers? Who knows...but you certainly got an in-depth look at what I picked out.

Although the front-end IC techies had treated the back-end packaging techies like serfs for the past 50 years, IFTLE tried to make it clear that the packaging community needed to stay up-to-date on what was going on in the front end, or we would be like blind people trying to paint portraits. In that vein, considerable time has been spent looking at what the front end was doing and the impact that could have on the back end.

Similarly, though I am not a design or test expert, I thought it was important to stay on top of the major design and test activities especially as we were trying to bring 3D ICs to commercialization.

From my 25+ years at Dow experience, which ranged from R&D through new product commercialization, I knew how long it took to get new concepts through the pipeline. Thus, while the commercial marketing houses like Yole Développement were out there proposing rapid market acceptance of advanced packaging like 3D TSV stacking technology, IFTLE was always throwing cold water on such inflated market numbers and short adoption time frames, which in hindsight has been very accurate.

My experience indicated that a proven concept in R&D usually takes at least a decade to reach its first \$1MM in sales. Again, in hindsight, 3D IC has taken even longer than that to gain commercial acceptance because of the enormous changes that were required in the infrastructure and business supply chain.

New things take time to really be understood and adopted, so when IFTLE found a technology that it thought could have a significant impact, we intentionally covered it multiple times to update and for reinforcement.

My best example of this would be Ziptronix and its direct bond interconnect (DBI) process.

Ziptronix spun out of Research Triangle Institute in 2001 without a primary application or a customer base. It took the Ziptronix team a while to realize that their oxide bonding process had relevance to CMOS image sensors (CIS), but once they did, the industry quickly adopted the technology and ran with it. While Toshiba was the first to adopt it in late 2008, licensee Sony has built their leading CIS market share on these oxide-oxide and copper-copper bonding technologies.

IFTLE has probably covered this technology 10 times or more over the decade. Our interest proved correct as we have recently seen all the major players (TSMC, Intel, Samsung, etc.) having what we now call "hybrid bonding" on their roadmaps to replace copper pillar bumps as we moved to ever-finer interconnect features. Was the commercial community waiting for the original Ziptronix patents to expire or was this simply a technology ahead of its time? I'll let you answer that.

Another technology that IFTLE has highlighted more than a dozen times is micro-transfer printing (MTP). It came out of a college laboratory in Illinois around 2005 as the start-up, Semprius. It is basically a massively parallel pick and place technology looking for an application. I worked with Semprius and its CEO Joe Carr (a long-time Dow colleague) in its early days but left when they decided to focus on manufacturing solar panels (IFTLE is NOT a fan of expensive energy sources).

While their solar efforts didn't succeed, the technology persisted and eventually spun out again as X-display, under Chris Bower, a company using the technology to move massive quantities of tiny LED components to fabricate LED displays. It has also become clear that MTP is also relevant to heterogeneous integration and, with the help of X-Fab, lives on as X-Celeprint. While MTP has not yet been included on the roadmaps of Intel, Samsung or TSMC just yet, my gut tells me there is something there and it will find larger applicability... eventually.

So what do I think have been some of the technical highlights that IFTLE has covered in the last decade?

#### General Observations:

- #1 is watching packaging evolve from an afterthought to the important position that it now holds in the overall industry.

- IFTLE has enjoyed watching long-time colleague Rao Tummala and his GaTech packaging center brethren bring microelectronic packaging into the educational mainstream.

- IFTLE has watched ASE's Bill Chen pour his heart and soul into the Heterogeneous Integration Roadmap. That kind of commitment is rare and should be applauded.

- IFTLE loved watching Peter Ramm and Mitsumasa Koyanagi **get the credit they deserved** for being pioneers in the development of 3DIC integration.

- IFTLE has watched Eric Beyne from his early days as a grad student to his status as a worldwide leader in advanced packaging.

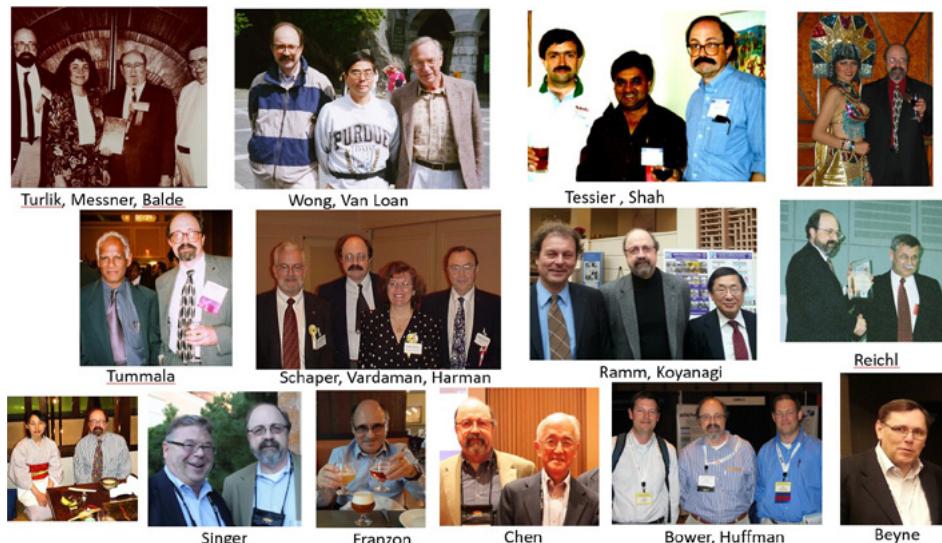

- IFTLE is thankful for having had the opportunity to have worked with advanced packaging colleagues like Jack Balde, George Messner, Avi Bar Cohen, Iwona Turlik, George Harman, Ted Tessier, Pete Elenius, Herb Reichl, Jan Vardaman, Paul Franzon, CP Wong,

[Continued on page 52](#)

**THE FUTURE IS CLEAR**

**Packaging for 6G Wireless Communications and Photonics**

**Thin Glass**

**Thin Glass with Custom Through-Glass Vias**

**Thin Glass with Custom Filled / Planar Vias**

**Metallized Thin Glass Wafer**

**MOSAIC**

**microsystems**

# Adaptive Control: The “Holy Grail” in Semiconductor Smart Manufacturing

By Dongkai Shangguan, Ph.D., Adaptix

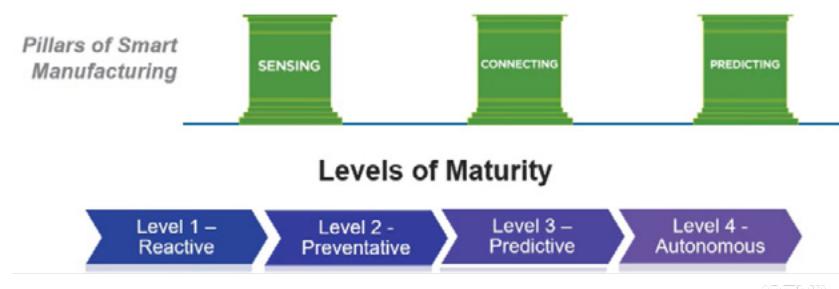

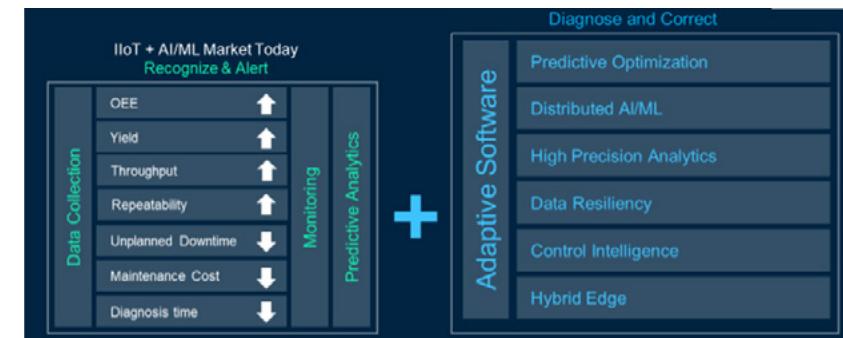

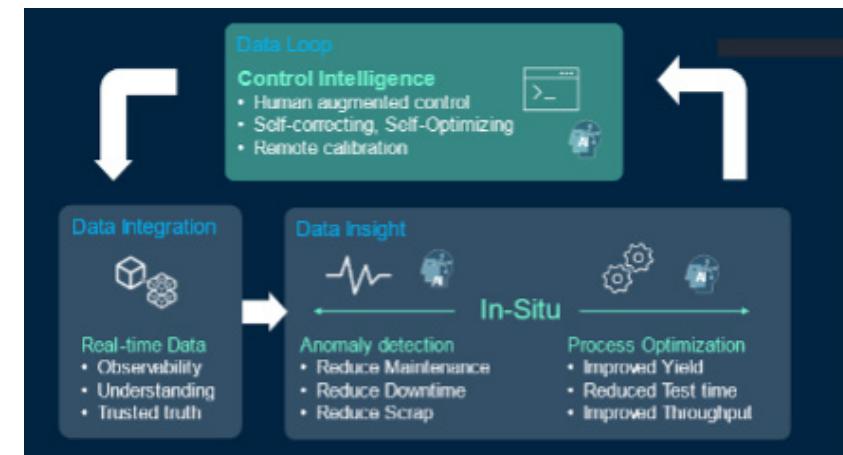

Artificial intelligence and machine learning (AI/ML) can have various applications in smart manufacturing for semiconductor fab, advanced packaging, and electronics manufacturing, and it typically involves several key elements: sensing, connectivity, predicting, and control. As recognized by many industry organizations, smart manufacturing matures through several levels: reactive, preventive, predictive, and autonomous (Figure 1).

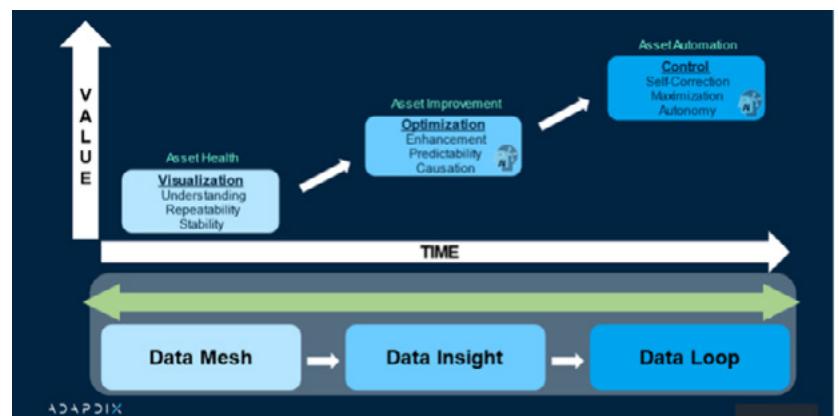

Adaptive control is the “holy grail” in AI/ML for semiconductor smart manufacturing. There are various AI/ML platforms in the industry that can be used for supply chain management, new product introduction (NPI), production planning, traceability, all the way to predictive maintenance, productivity improvement, process, and yield improvement, etc. The latest AI/ML platform can take you right to the highest level, with sensing, connectivity, predicting, and control all-in-one while providing a scalable, open, and cost-effective platform that seamlessly and progressively integrates all the key elements (Figure 2).

The AI/ML platform can utilize data from existing sensors within the machine, often without the need for additional sensors. The edge-first solution can integrate into other cloud and edge-based

services, allowing legacy system data connectivity to nearly all major automation vendor components and providing flexible data management tools to move OT data securely and reliably across complex enterprise edge-to-cloud network architectures. The ML models offer the capabilities for predictive optimization – for machine performance and the manufacturing

process, and its control intelligence capability can work directly with the machine, once approved by the customer, for adaptive control of the machine itself. As such, the AI/ML platform not only offers capabilities for observability and monitoring, but also further offers great capabilities for predictive analytics, optimization, and control (Figure 3).

Figure 1: Pillars and maturity levels of Smart Manufacturing (Source: SEMI).

Figure 2: Modules in AI/ML platform for different levels of applications (example).

Figure 3 Applications of AI/ML for electronics manufacturing (examples).

Fig. 4 Architecture of an AI/ML platform (example).

## Architecture

As an example, the software solution combines advanced AI/ML with a distributed, edge-based architecture (Figure 4). The platform connects and ingests multiple edge data streams (e.g., process logs, machine data, and instrumentation data in a time-synchronized fashion) in real-time – within millisecond cycle time. It can also collect full-stack data from the customer's end-to-end operations and perform real-time synchronization and validation of critical system data.

The flexible and containerized architecture can support a variety of protocols at the edge (including proprietary brownfield protocol deployments), thus allowing the platform to easily integrate with industrial equipment for data ingestion. The open and scalable architecture built specifically for the distributed edge environment can help avoid the overhead of moving all data to the cloud or centralization location from the get-go. The open and extensible architecture allows

[Continued on page 54](#)

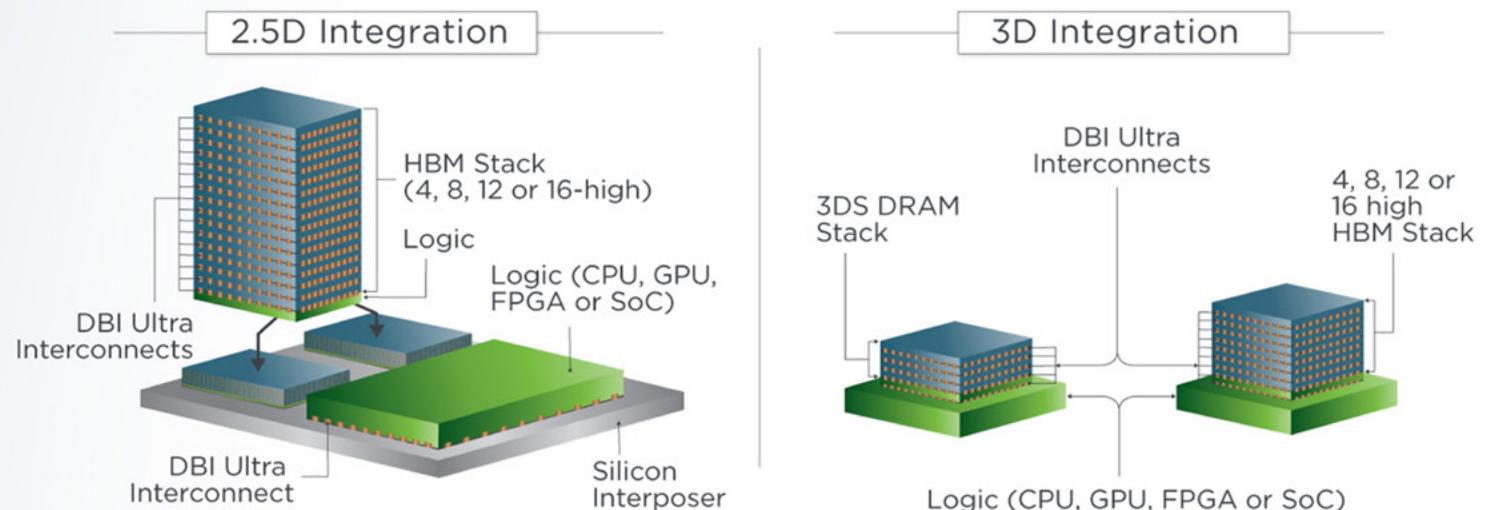

**DBI® Ultra**

Die to Wafer Hybrid Bonding

# Enabling Next-Gen High Performance Computing

Data Centers

Autonomous Vehicle

Gaming

## 3D Integration Technologies

**Ultimate Flexibility** in 2.5D and 3D integration of electronic circuits, for various die sizes, wafer sizes and technology nodes

## The Future of Semiconductors

### Ultra High Bandwidth with Fine Pitch Interconnect

### DBI Ultra Features and Benefits

- Scalable to 1µm Pitch 3D Interconnect

- No Copper Pillar or Underfill

- Thin Profile

- High Bandwidth

- High Bonding Throughput

- Low Temperature Process

- High Reliability

- Better Thermal Performance

- Low Cost

**DBI® Ultra** | Die to Wafer Hybrid Bonding

**DBI®** | Wafer to Wafer Hybrid Bonding

**ZiBond®** | Wafer to Wafer Direct Bonding

### Moving Beyond Moore's Law

[www.invensas.com](http://www.invensas.com)

# Looking Ahead to Inspire the Innovators of the Future

**A Conversation with KLA's Lena Nicolaides**

*By Françoise von Trapp*

2021 was a big year for the semiconductor industry, and 2022 is expected to be even bigger. Ironically, despite the mayhem it caused, the chip shortage and its impact on the global supply chain turned out to be the best advertising we could have hoped for in our industry. While those of us who work in the semiconductor industry once lived in relative obscurity, the whole world now knows how important semiconductors are to our everyday lives.

Semiconductor manufacturers all over the world are gearing up to meet demand by building new fabs and adding capacity to existing ones. The downstream effect is impacting global equipment and materials suppliers, as they too expand facilities and open new ones to ensure a well-oiled supply chain. The entire semiconductor ecosystem is in a hiring frenzy to support all this activity.

Well before the pandemic, industry seers predicted a strain on the semiconductor workforce as more engineers and technologists approach retirement age. At the same time, many of those just entering the workforce with degrees in science, technology, engineering, and math (STEM) are being drawn to what appears to be hipper, sexier STEM-related career paths. They dream of being part of the metaverse: Facebook. Google. Amazon. They want to design cool apps, pursue careers in biotech, or renewable energy. How can we interest them in something as "boring" as manufacturing tools or materials that make semiconductor devices? They didn't realize how cool it was to be part of the ecosystem that makes all these things possible. Until now.

## **Innovating a Talent Pipeline**

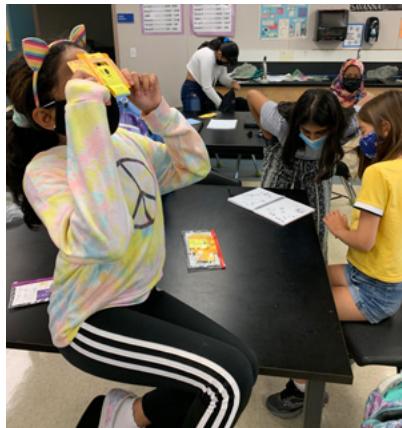

Where many people see challenges, Lena Nicolaides, Sr. VP and GM at KLA, sees opportunity (Figure 1). She is passionate about the semiconductor industry and the magic it makes happen. Early on in her role at KLA, Nicolaides spearheaded multiple efforts to promote STEM education. "We need innovators for the future," she says. She's made it her focus – leveraging her role at KLA – to inspire the next generation to not only pursue degrees in STEM but to parlay those degrees into careers in the semiconductor industry.

"Semiconductor CapEx is increasing at greater than 40% year-over-year growth. But without the talent nothing happens," she said. "We need innovators, and a lot of them, for the future of the industry."

As a company, KLA has always put a focus on talent, but now they are doubling down their efforts as the

situation becomes even more critical. But it's not enough to recruit new talent. How do you sustain it? How do you retain it? Nicolaides firmly believes the talent journey begins as early as elementary school.

"As we innovate for our tools, we innovate with our people," she says. "These are the people who create our systems. Starting the education process in elementary schools allows us to build a talent pipeline for innovators of the future."

She says it's exciting to go into classrooms and explain how KLA is one of the companies that enable the acceleration of chip production to address the current shortage. Because it impacts consumers'

ability to purchase everyday goods like new cars and appliances, young children now understand how important computer chips are.

"Making semiconductor technology relevant to the home has given us a fantastic opportunity. We need to leverage that so that we can attract talent. When parents talk about how they can't buy a car because of the chip shortage, it makes kids understand the importance of chips and want to work in the industry. We need to convey they can work on cool things like artificial intelligence (AI), and state-of-the-art optics and imaging technology. We need to show them how the industry can positively impact the environment by reducing energy use."

Figure 1: Lena Nicolaides and Stephen Hiebert, Senior Director of Marketing for KLA's LSA-SWIFT division, are passionate about the role KLA plays in innovation.

# The Great Resignation

In the aftermath of the pandemic, the US experienced what has been dubbed "The Great Resignation" as women and men of all professions took stock of their lives and made decisions about their careers that lead to record numbers of people leaving their jobs.

Nicolaides says that at KLA, and across the semiconductor industry, demand has increased. Part of that is because the industry is thriving and was also able to pivot to a virtual work environment.

"People have moved companies, some have taken early retirement, but overall, there is an increased curiosity about the industry," she said. "The pandemic has taught us all to retain our talent and flexibility is key."

For KLA, that meant working from home, working when you can, and showing up to a Zoom meeting with a child on your lap. "Flexibility and empathy empower the organization and make for happy engineers," she said.

Nicolaides also thinks that the pandemic equalized things. Zoom conferences on individual video screens, versus a conference call with a room full of people, brought people closer together and made it possible to build relationships with colleagues in other regions.

"It created a sense of equality in the way we do business and brought our divisions together," she said.

The semiconductor industry is testing a hybrid model blending work from home with work at the office allowing flexibility. As companies emerge from the pandemic, the work environment will further morph and evolve.

Figure 2: These 2μm resolution paper microscopes give students an idea of how tiny semiconductors can be, and the role electron microscopes play in the manufacturing process.

Nicolaides is especially proud of KLA's STEM Inspectors program that kicked off in 2019, in partnership with Santa Clara Unified School, Santa Clara, Calif, to bring STEM into the classroom (Figure 2). Using a hands-on approach with 2μm paper microscopes, students acquire useful STEM skills while learning how electron microscopes are used in the semiconductor industry. The pilot was so successful, it was launched globally, and already 1000 students have participated in it.

The breadth of career paths that a degree in engineering can open up is not readily apparent or rarely discussed. That's why, as part of the STEM Inspectors curriculum, students are introduced to the education paths and many career opportunities available in the semiconductor industry.

KLA supports multiple education programs and many of its employees invest their time to support and expand these programs. Examples include:

- **Science is Elementary** – KLA employees volunteer monthly to teach science modules to kindergarten students at Alexander Rose Elementary School in Milpitas.

- **First Robotics** – KLA Foundation sponsors over 20 high school robotics teams that compete in the annual FIRST Robotics Competition. Students learn how to design and build robots while

developing critical collaboration skills.

- **SEMI High Tech U** – As a Global Partner, KLA Foundation supports HTU efforts in helping students understand education and career pathways that lead to high-tech fields.

## One Person at a Time

Nicolaides remembers when KLA first hosted a module of SEMI HTU and how satisfying it was to see the sparks of interest light up. This outreach program offers three-day experiences to high-school students who are interested in pursuing careers in STEM. The students participate in hands-on workshops and group challenges to learn about STEM-related fields. They visit manufacturing facilities, learn how to write a resume, and participate in mock interviews.

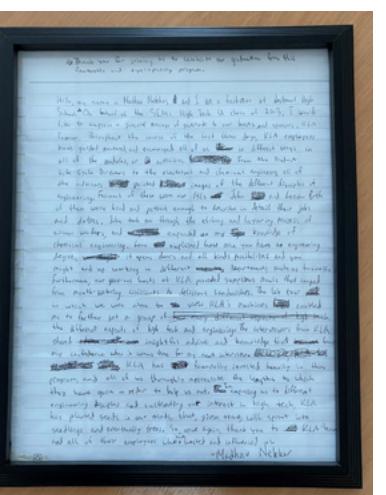

Madhav Nekkar, a freshman at Westmount High School, was so inspired by what he learned, he wrote a personal letter to Nicolaides expressing his gratitude to KLA for hosting the event in 2013. He went into detail describing the experience, and how it planted a seed to pursue a degree in STEM. She had his letter framed and it hangs on the wall in her office as a reminder that if you can reach just one person, the effort is worth it (Figure 3). Madhav graduated with a STEM degree and is now working in the industry.

Figure 3: Nicolaides proudly displays this thank-you letter from SEMI High Tech U graduate, Madhav Nekkar, to remind her that even reaching one person makes the efforts worthwhile.

## The Gender Gap

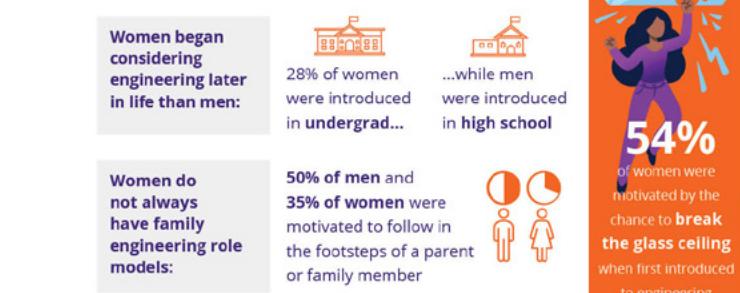

Even with industry-wide initiatives underway, gender inequality continues to plague the semiconductor industry. According to a global survey of engineering students and career engineers, women tend to seek a career path in engineering later than men. A higher percentage of male engineers set out to become engineers while still in high school, while women decide as undergrads (Figure 4).

Again, Nicolaides believes the problem can be traced back to elementary-age children, who are generally given conventional gender-defined toys. Puzzles, train sets, and Legos are listed under "Boy's Toys", while dolls, toy kitchens, and Easy-Bake Ovens are listed as "Girls Toys".

For its part, KLA works to create opportunities and increase long-term access to educational resources to support girls and under-represented communities throughout their unique journeys, including STEM fields. By supporting Taiwan Girls Camp, Habitat for Humanity, and Alliance 4 Girls, KLA provides resources for young girls and women to overcome the challenges of gender inequality.

Helping the gender gap at all levels within KLA, Nicolaides is the executive sponsor for the Women in STEM Empowered (WISE) employee resource group (ERG) that works to attract, advance, and provide more opportunities for women at KLA. WISE helps KLA's employees grow and navigate their development path at KLA.

## A Career Born out of Curiosity

"The curious mind will gravitate towards STEM," says Nicolaides.

## Women seek an engineering path later and are perseverant.

Figure 4: Data show that women seek an engineering path later and are perseverant.

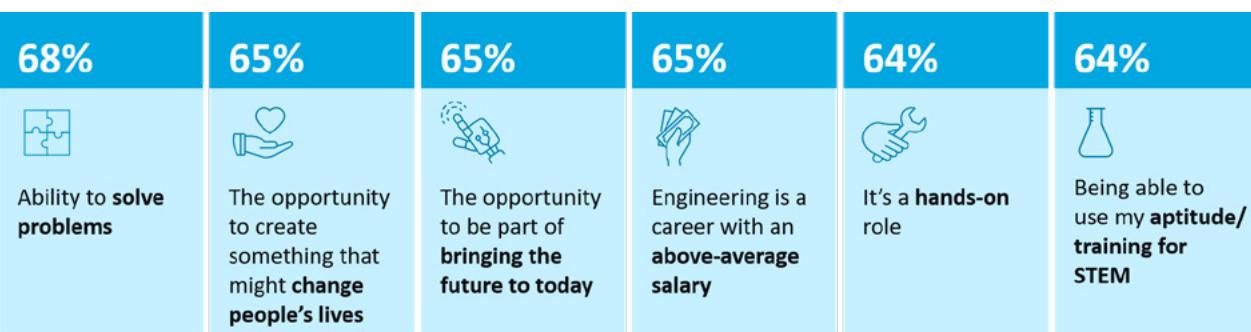

According to **KLA's Engineering Inspiration Report**, engineers today are inspired by purpose and technology: Things like the digital era, sustainability, and social and societal issues (Figure 5)

Nicolaides often draws on her 20-year career in the industry, and specifically at KLA, to illustrate the wonder of the semiconductor industry. She says she's never bored and continues to be inspired to innovate.

"Building these tools – inspectors that find these small, tiny things – it's so fulfilling to see a tool go into production," she says. "As engineers, we all have in common the desire to see our ideas come to fruition."

She thinks many people underestimate how big engineering is and how many fields there are. People can start as engineers and go on to have a very diverse career path. For example, Nicolaides began as a research scientist and is now a general manager.

With a foundation in STEM, the semiconductor world is your oyster – from R&D, processes and technology, to operations,

sales, support, and beyond. Do you want to travel the world? Work in cutting-edge technology? Move to marketing? Be a writer? Climb the corporate ladder? The semiconductor industry has it all.

"There is a role for every personality within our semiconductor industry," says Nicolaides. "From engineers to marketing, to technicians, application engineers, human resources, corporate roles... tell me your degree, and there's probably a job you can have."

## Sustaining and Retaining Talent

"How do we strengthen our talent? We enable them to grow from within," says Nicolaides. "Retention starts from Day One." She identified three keys to retention.

## Open Communication

"Employees want to feel like they are part of something bigger," notes Nicolaides. If they fully understand the mission and goals of their division and the outcome of their work, they have context and are more likely to stay with the company. Alternatively, companies who silo their employees to protect their IP,

Figure 5: When first introduced to engineering, around two-thirds of engineers and students were highly motivated by the ability to solve problems, the chance to change people's lives, and the opportunity to bring the future to today.

tend to see less commitment. And during the pandemic, more frequent communication was needed to enhance transparency and strengthen the team connections.

#### Ongoing Development

"It's important to be at a company that develops you," says Nicolaides.

At KLA, this means professional development, continuing education, and ERGs. For example, the WISE ERG holds regular events.

One recent panel discussion focused on how to navigate your development path at KLA. One employee talked about first working on the development of one inspector system, and then followed that with a role in the applications division,

leveraging the knowledge gained during tool development. Another employee described their journey from engineering into a marketing role.

They also have an in-house learning center where new hires follow a standard curriculum and have access to a wide range of training courses as part of their KLA career path. Employees can take advantage of other enrichment programs and pursue master's degrees.

#### Show Appreciation

The third element on the continuum of retention is to show appreciation. KLA regularly celebrates employee achievements. It's the little things that go a long way. Appreciation is

shown, with several award programs, at both individual and team levels. The pandemic further demonstrated the need for appreciation and connecting with team achievements.

"It's about understanding the talent you have, and empowering the talent you have," said Nicolaides. "That is how you inspire others to follow this path."

#### Conclusion

From kindergarten to a career at KLA, inspiring the innovators of the future is a lengthy and complex journey. But industry leaders like Nicolaides understand that it's worth every step. The key to success is to keep looking ahead.

The new Plus Building at the KLA Milpitas campus has room to host large employee meetings, a modern cafe with rooftop patio and ample space for employee collaboration.

On-site coffee shop at the KLA campus in Milpitas

Convertible walls can open and let the California sunshine into the new multi-purpose space at the KLA headquarters.

## Enhancing Surfaces and Materials for the World's Technology Leaders

Production-Proven HVM Systems for Wafers, Panels, and Advanced Substrates

### Thermal

- Low-temp curing

- High-vacuum curing

- Degas and dehydration

- Fluxless solder reflow

- UV and thermal curing

- Hybrid bonding

### VertaCure™ XP

High-volume automated system for polyimide vacuum cure

### Coating

- Monolayer coating

- Monolayer coating with in-situ plasma cleaning

- LPCVD coating

### Wet

- Plating (electrolytic and e-less)

- Clean and surface prep

- Desmear

- EBR

**Yield Engineering Systems, Inc.**

Call: 1-510-954-6889 (worldwide) or 1-888-YES-3637 (US toll free)

[www.yieldengineering.com](http://www.yieldengineering.com)

# Considerations in Power Amplifier Package Design

By Casey Krawiec, StratEdge

## Understanding the role of compromises and trade-offs in the design process

Electronic packages serve many purposes including protecting, connecting and cooling a device. If any of these are done improperly, the chip is rendered inefficient at best or useless altogether. For that reason, the design, construction, properties, and capabilities of the package selected are critical to ensure optimal device performance.

Temperature is one of the main factors that affect performance. High-frequency devices can suffer a loss of efficiency as temperatures at the chip level increase. Every degree of heat that can be dissipated adds to the efficiency of the device as well as to its useful life.

The package plays a significant role in thermal management. Proper thermal management is essential for high frequency and high-power semiconductor devices such as gallium arsenide (GaAs) and gallium nitride (GaN). In particular, GaN-on-SiC devices have incredibly high power densities and the design of the electronic package can dramatically affect their performance.

Several types of engineers are typically involved in the electronic package design cycle. Mechanical engineers, materials engineers, electrical engineers, and thermal engineers contribute most often, but sometimes manufacturing or industrial engineers might also be included. So, the compromises and trade-offs begin at the engineering level but don't end there. People from the accounting, quality, purchasing, assembly, and sales and marketing departments may also have input.

Within this assortment of people that have such different levels of education, experience, and expectations, it can be difficult to

please everyone. The person in charge of the final package design, more often than not, feels pulled in a lot of different directions. But if everyone understands that many issues beyond their own must be considered, the team can achieve a workable design that meets the customer's major objectives.

## Package Layers

Thermal considerations address two areas, thermal expansion, and thermal conductivity. A useful tool in considering electronic package designs is to consider the package as a series of stacked layers. Working with and thinking about packages in terms of layers can simplify thermal dissipation and expansion analysis. Viewing packages as layers is a useful way to understand 3D interactions in the package structure. This is the basis for thermal simulation modeling.

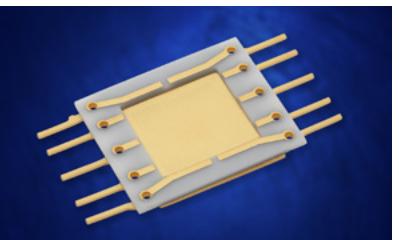

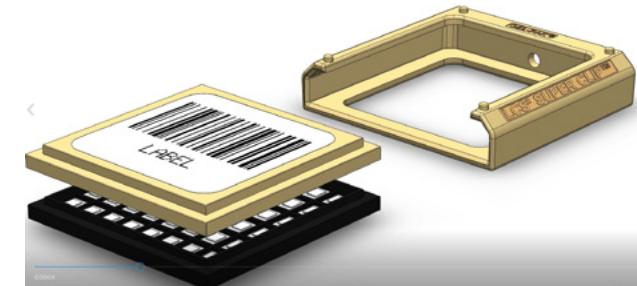

The leadless power amplifier (LPA) package is an example of layered construction. It begins with a combination base and heat sink, topped by an alumina insulating layer, a metal lead frame, and a lid. (Figure 1.)

The surface mount power (SMK) package is very similar to the LPA package but has vias to carry the signal from the top conductor pads to the bottom of the package. The leads on the bottom of the ceramic are coplanar with the bottom of the base. With the leads trimmed short, this package is appropriate for surface mounting (Figure 2.)

Figure 1. LPA Package.

Figure 2. SMK Package.

over a broad range of frequencies. LPA packages have excellent performance from DC to 23 GHz and have bolt holes for securing the package to the printed circuit board (PCB) and chassis. SMK packages operate from DC to 26 GHz and have the convenience of being surface mounted, which simplifies the PCB design.

## Conclusion

Many factors need to be considered when designing the optimum power amplifier package, including thermal dissipation and expansion requirements. Usually, no single consideration can dominate, so the design decisions end up as compromises. One simple method to aid understanding of the issues in assembly and function of the package is to view the package as layers. This simple analysis is useful to understand both the CTE and heat flow. Simulation tools can be used to analyze the impacts of expansion mismatch and thermal conductivity on the reliability and performance of the final assemblies. These tools can be used to estimate if material choices are practical and to what degree a material or design change will impact a performance parameter of the package.

SIEMENS

Reduce your IC design cycle time by 30%

Learn how to trade up to Xpedition Package Designer (xPD) xPD is designed for the physical design, verification, and modeling of emerging High Density Advanced Packaging (HDAP) technologies

Siemens EDA

Your Complete Solution for IC Packaging Design & Verification

# Vehicle Electrification Driving Supply Chain Evolution

Dr. Ajay Sattu, Amkor Technology, Inc.

If the recently concluded CES® 2022 is any indication, the automotive industry is yet again in the crosshairs of both consumers and industry experts alike. Whether it's the new electric vehicle (EV) model introductions, color-changing technologies, or concept cars, automotive companies are slowly transforming themselves from manufacturers to technology platform providers. Vehicle electrification is one of those megatrends that has now morphed from a novel trend to accepted reality. Several environmental, economic, and social factors are influencing vehicle designs and the new powertrain choices. However, some of these choices and corresponding component design and manufacturing aspects may lead to a supply chain evolution in the coming years.

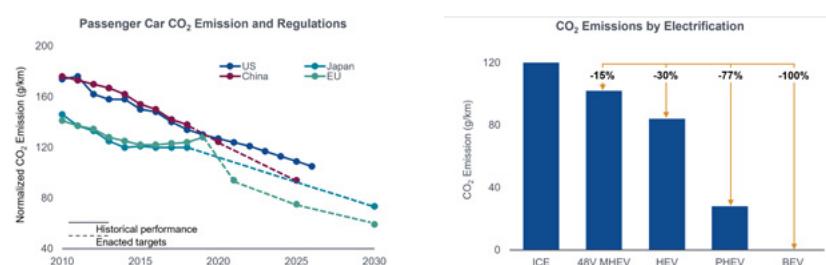

Figure 1: CO2 emission standards and vehicle electrification<sup>4</sup>.

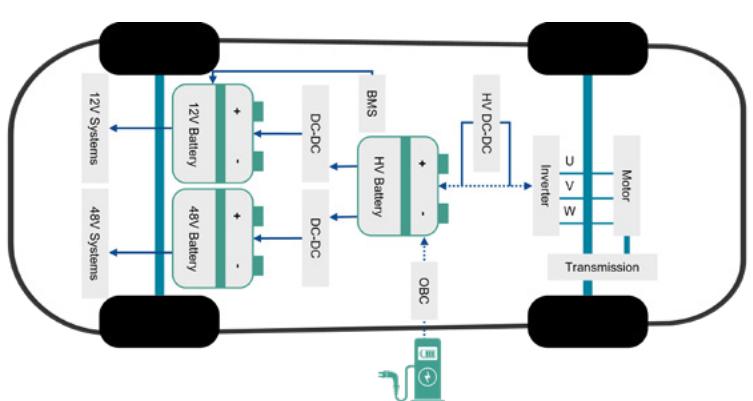

Figure 2: Simplified schematic of an EV powertrain.

## Market Trends

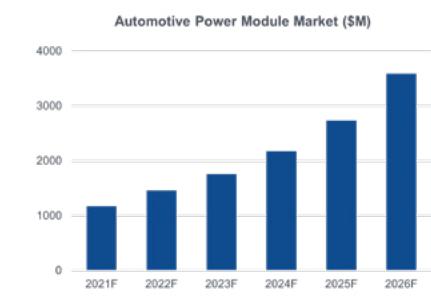

CO2 emission mandates set by various regulatory agencies are driving electromobility growth. For example, as shown in Figure 1, the chart on the left shows normalized CO2 emissions for each of the four major automotive markets, while the chart on the right shows how CO2 emissions can be reduced by various degrees of electrification. The internal combustion engine (ICE) has nearly 100% carbon emissions. In contrast, mild hybrid electric vehicles (MHEV) use a small motor to aid the ICE, providing a 15% emissions reduction. A battery electric vehicle (BEV or EV) uses only a DC battery and motor and thus produces no carbon emissions. Through various powertrain architectures and proliferation, within the next five years, nearly 25% of all vehicles produced will be electrified with the

number increasing to around 50% by the end of 2030<sup>1</sup>. This huge growth is due to increases in expected demand, reductions in the cost of the DC battery, and anticipated growth in the charging infrastructure.

As a result, power semiconductors used in EV powertrain systems will see huge growth. To better understand this growth, let's examine a simplified schematic of an EV powertrain (Figure 2). The critical blocks that enable the main functionalities are the onboard charger (OBC), DC/DC converters, and the main inverter. The critical components that enable each of these circuits are power devices, used as switching elements. At the system level, a key priority for EV designers is maximizing the efficiency of all these circuits to enable a better range between each battery charge. As the system requirements increase, so do the requirements on the cost (\$/kW) and power density (kW/l) of the power electronics. Currently, cost targets are roughly 5 \$/kW, whereas power density is around 12 kW/l. These targets are expected to reach 3 \$/kW and 60 kW/l by 2035<sup>2</sup>. To achieve these goals, semiconductor suppliers need to offer superior solutions including newer power technologies such as silicon carbide (SiC) and gallium nitride (GaN) devices, and use cost-efficient power module packages.

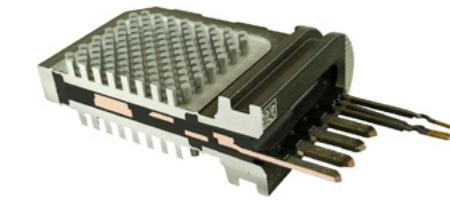

## Power Module Packaging

In main inverter applications, power modules must address performance and reliability targets within thermal, electrical, and mechanical constraints. While the bulk of the electrical performance is addressed by the semiconductor devices, power module packaging plays a vital role in meeting the thermal and mechanical targets. However, electrical performance

Figure 3a: Double-sided cooling molded module cross section. Figure 3b: Power module with pin-fins for direct cooling [5].

can also be improved by reducing parasitic resistances (R) and stray inductances (Ls) of the package. Ls is especially important to reduce overshoot voltages during switching; Ls of a power module results from the substrate metal parts, wire bonds, and lead frame/bus bars. One of the ways to minimize these losses is to reduce the current loop geometrical length and area. Wire-bond-free concepts such as double-sided soldering and sintering on ceramic substrates are better solutions to lower Ls. One such solution, a double-sided cooling (DSC) molded module, is shown in Figure 3a, where wire bonds are replaced with sintering for the current path between collector and emitter of the insulated gate bipolar transistor (IGBT) switch. The DSC module structure not only reduces the electrical parasitics but also offers enhanced thermal efficiency by removing heat from the top and bottom sides of the package through the substrates.

Power cycling and higher ambient temperatures subject power modules to large temperature excursions. So, a cooling system that does not complicate system design and increase cost becomes increasingly important. One way to address these concerns is power module designs with pin-fins (Figure 3b) that share the cooling system used by the motor or engine. For extended reliability, heat must be dissipated effectively, which can only be achieved using low thermal resistance materials. Higher thermal conductivity ceramics such as aluminum nitride (AlN), silicon nitride (Si3N4), and copper (Cu) with a direct cooling structure can be used to reduce the overall thermal resistance. Whether it is a baseplate-free solution such as a DSC module or a pin-fin power module, the packaging industry needs to

consider several technologies for next-generation power modules. These include interconnection advancements such as thick gauge (>5 mil) Cu wire, Cu clips, advanced substrates such as Si3N4 with active metal brazing (AMB), die-attach and substrate attach using silver (Ag) or Cu sintering, Cu or AISiC baseplates, and silicone gel or epoxy resin encapsulation.

In situations where traditionally closed geographical ecosystems existed, some suppliers have started to diversify their business or regional portfolio. The geographical expansion has increased to take advantage of packaging technologies such as substrates, die-attach, and encapsulation.

The automotive industry has long been a high-volume, low-price arena. With the growth in the power module market, competition will increase and suffer from price pressures leading to partnerships to reduce costs and simplify market entry. On the positive side, module technology is well understood, and suppliers have known to release products with excellent performance and reliability. For non-power module makers such as outsourced semiconductor assembly and test (OSAT) suppliers, entering the power module market presents an appealing case since they can easily leverage their current expertise in ramping products to high volume with proven reliability and an appealing cost structure. One final factor that is favorable for OSATs is automakers increasing willingness to venture deep into the supply chain for the inverter module design to differentiate themselves from competitors and to control costs.

**Continued on page 56**

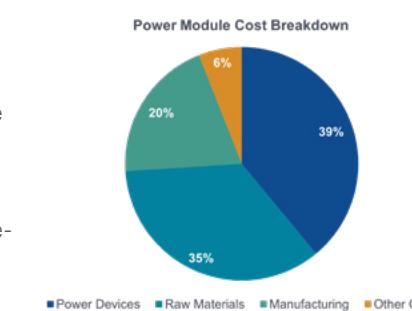

Figure 4a: Power module cost breakdown<sup>3</sup>. Figure 4b: Automotive power module market (in \$M)<sup>3</sup>.

# Through The Eyes of Our Interns